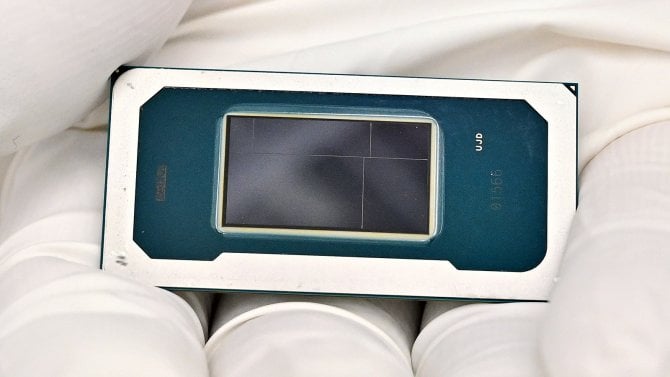

Minulý měsíc se na poli výrobní technologie polovodičových čipů objevila zajímavá zpráva a o plánech firmy Samsung – ta ohlásila někam do příští dekády 4nm technologii, která přinese zcela nový typ tranzistoru MBCFET jako náhradu za FinFETy používané od 22nm–14nm procesu. Stejnou cestu vývoje bude zdá se sledovat i polovodičová divize IBM, která nyní patří pod GlobalFoundries. Tyto tři subjekty na vývoji dlouhodobě spolupracují a tak nejde o nic překvapivého. IBM však chystá nový typ tranzistorů už na 5nm proces, na němž nyní také demonstrovalo první zkušební čipy.První 5nm čip je zatím jen testovací a do produkce je ještě daleko, ale i tak jde o významný milník. Důležitější než samotné číslo je však demonstrace onoho nového typu tranzistorů. Technologie IBM (na výzkumu kromě něj spolupracují i GlobalFoundries, Samsung a Polytechnický Institut Státní univerzity New York) jim neříká MBCFET jako Samsung, nýbrž GAAFET. Princip by ale měl být podobný, ono GAA totiž znamená pojem „gate all around“, který používá i Samsung. MBCFET by mělo být jen pojmenování konkrétní struktury, kterou Samsung princip GAAFET na čipech implementuje.

Opět nanodestičky

Tranzistor GAAFET v podání IBM nahrazuje vertikální kanál tranzistoru FinFETu štosovanou soupravou nanodestiček, které jsou uložené horizontálně postupně nad sebou. Kanál tranzistoru tedy bude zněkolikanásobený – pokusný čip má zřejmě tyto nanodestičky nad sebou tři, ale teoreticky by jejich počet mohl být i vyšší. Aby se dal kanál efektivně uzavírat, jsou nanodestičky ze všech stran obklopeny materiálem řídící brány, což je klíčová novinka tohoto uspořádání.

Díky tomu vliv brány snáze proniká dovnitř, jelikož nanodestička je tenká. Oproti tomu monolitický kanál FinFETu měl mnohem větší průřez a brána ho navíc mohla obklopovat maximálně ze tří stran, nikoliv zespodu. GAAFET proto slibuje dokonalejší fungování a schopnost pracovat na nižších napětích a s menšími únikovými proudy – a díky tomu umožnit škálování křemíkové technologie na 5nm–3nm procesy, kde by FinFETy asi už narazily.

Výroba těchto 5nm čipů probíhá pomocí litografie s EUV (záření extrémně ultrafialového spektra s výrazně nižší vlnovou délkou než dnešní 193nm světlo). Ta ještě dnes není komerčně dostupná, ale má být nasazena během 7nm generace, takže pro 5nm proces už by měla být připravena. Zároveň je – aspoň v této fázi – vyžadováno použití technologie SiGe, tedy křemíku a germania. Vrstvy SiGe a křemíku jsou nejprve uloženy, poté jsou v nich „vyryty“ základní struktury, poté jsou některé vrstvy odstraněny a mezery později opět vyplněny.

Postup formování vypadá velice složitě a pravděpodobně nebude nijak levný, i když EUV pomůže omezit počet potřebných expozičních kroků a masek. Nicméně pro produkční nasazení asi bude snaha metodu ještě nějak zjednodušit – to by v budoucnu možná mohlo zajistit uložení nanodestiček do vertikálního štosu místo horizontálního. Zda IBM/GlobalFoundries počítá se stejnou strukturou jako u těchto testovacích čipů také pro masové nasazení, to zatím nevíme.

40% zvýšení výkonu proti 10 nm

Predikce výkonu čipů na těchto budoucích procesech jsou vždycky problematické, nicméně IBM uvádí, že v porovnání s 10nm čipy (asi Samsungu) má při stejném výkonu být dosažitelná 75% úspora spotřeby (jde o skoku o dvě generace, takže nejde o úplně nehorázný příslib). Při stejné spotřebě pak má být možné zlepšit výkon o 40 %. Hustota tranzistorů má také být zhruba o 50 % lepší než u 7nm procesu IBM (pro který IBM demonstrovalo první pokusný čip před dvěma lety, bez jednoho měsíce).

Co je ještě na této technologii zajímavé: šířka nanodestiček je díky jejich horizontální poloze „ovladatelná“. Plochu tranzistoru (a tím průřez kanálu) lze tedy v návrhu čipu měnit podle toho, jak velké požadavky na jeho zatížení budou. U FinFETů tato schopnost není kvůli vertikálnímu uložení „destičky“ tvořící jeho kanál.

Kdy by se tento proces mohl dostat do výroby, zatím nevíme. GlobalFoundries u 7nm technologie počítá se zkušebním provozem a tapeouty letos a startem komerční výroby do konce roku 2018; 5nm proces by tak asi byl nejspíše záležitostí roku 2020 či 2021.