O víkendu jsme tu psali o XL-Flash, speciální paměti NAND pro výkonnější aplikace, kterou odhalila Toshiba na Flash Memory Summitu. Na stejné akci se toho sešlo víc a novinku se speciálním označením prezentoval také Hynix. Má to být paměť označená 4D NAND, což implikuje nějaký další pokrok proti v současnosti už etablované technologii vrstvených pamětí NAND, které se obecně označují jako 3D (trojrozměrná) NAND. Pracovat v čtvrtém rozměru pochopitelně Hynix nebude, takže jde hlavně o marketing, ale něco nového tato technologie skutečně přináší.

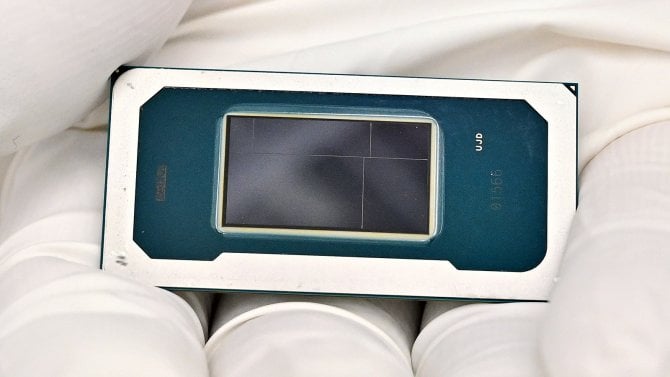

4D NAND bude u Hynixu obchodní nálepka pro novou generaci jeho pamětí NAND, jde tedy stále o klasickou technologii pamětí Flash – v tomto případě je založená na paměťové buňce typu tzv. charge trap. Konkrétní zlepšení, která má označení 4D NAND reprezentovat, se ale nenachází v samotné soustavě záznamových buněk, ale v infrastruktuře, která je obsluhuje.

Flash potřebuje své komunikační rozhraní a také infrastrukturu, která obsluhuje vrstvy se záznamovými buňkami. Tyto bloky jsou na čipu NAND netriviální a zabírají slušnou plochu. Obvykle jsou někde po straně nebo samotnou paměť obklopují dokola, takže se jim říká „periférie“. Důležité je, že jde o logické obvody a netýká se jich technologie vrstvení NAND, jsou klasicky jednovrstvé. A to je problém, protože zatímco hustota záznamu samotných buněk se dá pořád navyšovat přidáváním dalších a dalších vrstev, periférie s nimi neškáluje a její plocha se tak nezmenšuje. V extrémním případě by to dokonce mohlo vést k tomu, že by se stávala větší a větší částí plošné rozlohy čipu a tím ho vlastně prodražovala, protože o tuto plochu se zhoršuje škálování kapacity v samotných blocích NAND. Periférie tudíž přidává k ploše čipu NAND a snižuje množství čipů (kapacity v GB), které se dají vyrobit z jednoho waferu.

Obslužné logické obvody ve zvláštní vrstvě

Aby se čipy mohly zmenšit a zlevnit, přišel proto Hynix s řešením, kdy se tato periférie přesune do samostatné vrstvy, která pak může být uložena pod vrstvy s bloky NAND, čímž se plocha těchto logických obvodů „schová“ a půdorys čipu je hned menší. Implementace je samozřejmě o dost složitější problém, ale Hynix zdá se tento úkol vyřešil a jeho příští generace NAND bude tuto koncepci nazývanou „Periphery Under Cell“ aplikovat v praxi. Označení „4D“ má reflektovat právě tuto změnu proti předchozí 3D NAND s periférií okolo bloků NAND („Cell“).

Koncepce Periphery Under Cell a a tím i 4D NAND se poprvé objeví v páté generaci vrstvených čipů od Hynixu („V5“). Ta má obsahovat 96 vrstev NAND, takže ovládací logika by asi mohla představovat 97. vrstvu. První vzorky těchto čipů mají být dostupné už letos, v Q4 2018. Má jít o TLC čipy s kapacitou 512 Gb (64 GB) pro jednočipová úložiště třeba typu eMMC; v Q1 2019 pak přibude také 1Tb (128GB) čip pro běžná SSD, také typu TLC. To není bez zajímavosti, protože momentálně se kapacita 1 Tb objevuje se záznamem typu QLC.

Hynix chystá i QLC NAND

Tuto technologii Hynix zatím na trhu nemá (na rozdíl od Toshiby, Sasmungu a Intelu/Micronu, kteří už ji uvádějí nebo uvedli – viz čerstvé Intel SSD 660p), ale podle zpráv z Flash Memory Summitu na QLC NAND také pracuje, takže v budoucnu se od něj tohoto typu NAND dočkáme také. Vzroky jeho QLC čipů mají být dostupné v druhé polovině roku 2019, takže v praxi se s nimi setkáme asi až v roce 2020. Také tyto čipy mají používat technologii 4D NAND.

Podobnou technologii už používá Intel s Micronem

Zde je ještě třeba říct, že ačkoliv na 4D NAND si asi Hynix pořídí ochrannou známku a ostatní výrobci toto označení nepřevezmou, koncepce Periphery Under Cell nebude pro tuto firmu unikátní. Samsung ji nyní studuje také a v budoucích variantách své „V-NAND“ by ji měl aplikovat také. A paměti NAND Flash od Micronu a Intelu dokonce zdá se už tuto technologii mají nyní, snad již od první generace jimi vyvinuté 3D NAND– ovšem v jejich podání to nese jméno CMOS under Array.

4D/3D NAND může mít až 500 vrstev

Koncepce 4D NAND s logickými obvody pod buňkami má pak Hynixu vydržet i v dalších generacích, přičemž následující šestá generace vrstvených NAND má již mít 128 vrstev. Podle Hynixu může jinak počet vrstev v 3D/4D NAND obecně růst ještě hodně dlouho, reálných je dle odhadů firmy třeba až 500 vrstev. Pochopitelně ale až někdy v budoucnu, k těmto metám povede postupný vývoj.