Procesory ARM, ovládající dnes mobilní zařízení, už se nějakou dobu snaží dostat do serverů. V předchozích letech této dekády v tom ještě moc úspěšné nebyly, ale letos se dostala ven první CPU založená na architektuře ARM Neoverse N1 (Graviton2, následovaný Ampere Altra), která už měla docela velký ohlas.

Teď ARM oznámil další generace svých serverových architektur pro následující léta, které opět slibují agresivní zvýšení výkonu a měly by ještě zvýšit tlak na Intel (a AMD). Je možné, že tyto platformy už začnou výrazně ukusovat z podílu architektury x86 na trhu, ale samozřejmě teprv uvidíme, jak se slibované pokroky přenesou do reality.

ARM povede útok na dvou křídlech

Současná architektura Neoverse N1 odvozená od mobilního Cortexu-A76 nekonkuruje zatím procesorům x86 v maximálním jednovláknovém výkonu. Je podobně jako Cortexy navržená tak, aby dosahovala vysoké efektivity co do spotřeby a plochy, kterou jádro zabírá.

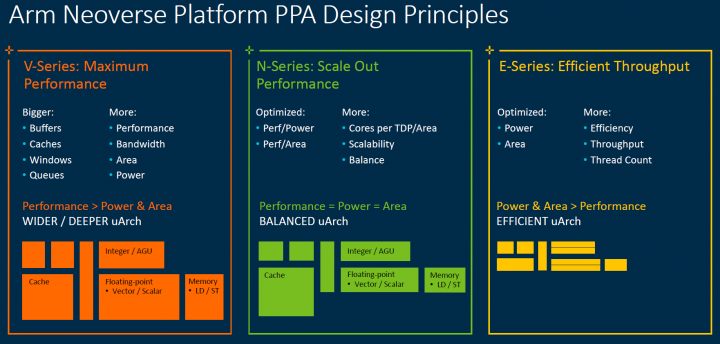

Tato strategie ovšem trošku ARM držela zpátky. Nyní proto nastupuje jiná a ARM bude mít dvě architektury. Jedna bude pokračovat v cílení na vysokou efektivitu, a bude tedy x86 ohrožovat vyšší úsporností, druhá se ale těchto limitů zbaví a půjde po absolutním výkonu, který by jinak byl výhodou Xeonů/Epyců. Zákazník si bude moci vybrat a specializace na jeden ze scénářů by měla být výhodou proti X86, kde Intel a AMD mají pro oba to samé univerzální jádro.

ARM Neoverse V1: maximální výkon

Architektura, která z nové generace serverových jader ARM bude zaměřená na absolutní výkon, se oficiálně jmenuje Neoverse V1. Není úplně překvapivá, v roadmapě už byla dřív vyznačená pod kódovým jménem Zeus. To není úplně náhodné – je totiž podobná jádru ARM Cortex-X1 (kódové označené Hera). Cortex-X1 také míří na vysoký výkon, i do nějaké míry na úkor energetické efektivity, takže v tomto si s V1 odpovídají. Nicméně jádro V1 bude mít svoje odlišnosti, nejde o stejnou architekturu.

Procesory s architekturou Neoverse V1 již mají typicky podporovat PCI Express 5.0 a používat paměti DDR5; ovšem také u nich bude možné použít jako mezistupeň velmi rychlé paměti HBM2e. Na platformě bude také podporované propojení CCIX 1.1, ale ještě ne CXL.

Podle ARMu budou typicky zákazníci s jádry V1 stavět procesory s 64 až 96 jádry. Jako o prvním kandidátu víme o firmě SiPearl, která připravuje serverové/HPC procesory pro projekt lokálních superpočítačů v EU – její čip kódově označený Rhea má 72 jader Neoverse V1 v mesh uspořádání. 4–6 kanálů DDR5 a bude opravdu používat paměti HBM2e jako cache s vysokou propustností.

Tip: Evropské procesory EPI pro superpočítače použijí ARM Neoverse, RISC-V na 6nm procesu

SVE

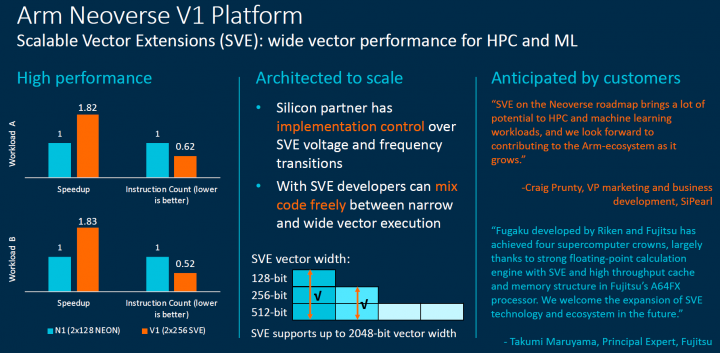

Důležitý element bude přidání podpory SIMD instrukcí SVE (to je právě jedna z odlišností proti X1). To je pokročilejší vektorové rozšíření zaměřené na HPC (výkonné výpočty, superpočítače). Zatím SVE používala jen HPC architektura Fujitsu, ale s příští generací instrukční sady ARMv9 možná bude ve všech jádrech coby součást standardu. Jádro V1 ještě není ARMv9, ale jen ARMv8, nicméně instrukce SVE již má. V jádru by měly být dvě SIMD pipeline se šířkou 256 bitů (tedy jako u AVX/AVX2).

Neoverse N1 ještě mělo jen instrukce Neon se 128bitovou šířkou, které jsou srovnatelné s SSEx na platformě x86, takže toto je značné zlepšení. Ovšem samozřejmě bude nutné, aby SVE začaly využívat programátoři, přidali tento kód do svých projektů, nebo aspoň použili autovektorizaci. Tam, kde se autovektorizuje kompilátorem, to může být celkem snadné a automatické, v multimédiích (FFmpeg, x264/x265 a další enkodéry) to typicky bude vyžadovat ruční přepsání v asembléru. Mimochodem, kromě SVE budou podporovány také výpočty s hodnotami bfloat16 pro AI.

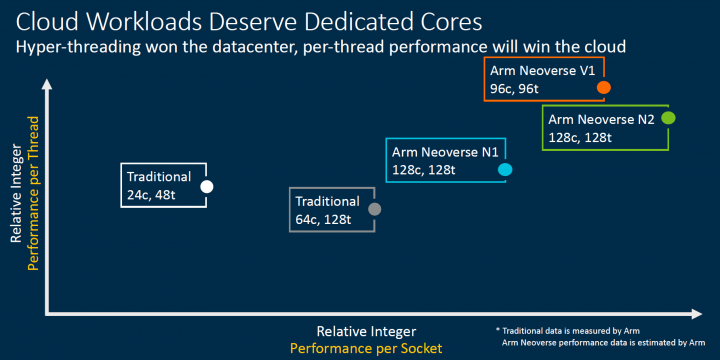

Pořád bez SMT

Co procesory pořád nemají, je SMT, jedno jádro tedy stále bude jen jedno vlákno. Toto nechává nějaký potenciální výkon jednotek v jádře nevyužitý, ale ARM se vyhne sdílení jader různými procesy/uživateli (problém v cloudovém využití) a absence SMT výrazně usnadňuje návrh a validaci architektury. Plus se samozřejmě zmenší plocha jádra.

+ 50 % IPC/výkonu jednoho jádra proti dnešku

ARM Neoverse V1 má proti jádru N1 mít až 50% navýšení jednovláknového výkonu, ale poté je řečeno, že je to na stejném procesu a při stejné frekvenci, takže by šlo přímo o 50% zlepšení IPC. ARM počítá s tím, že tato jádra se budou realizovat na 7nm nebo 5nm procesu, takže možná nad rámec tohoto budou i nějaké frekvenční zisky z 5nm technologie.

ARM uvádí, že podle jeho očekávání budou procesory s těmito jádry výrazně napřed před tím, co dnes nabízí AMD a Intel na bázi x86, alespoň v celočíselných zátěžích. FPU a SIMD jednotky tedy asi pořád nebudou mít takový výkon proti AVX-512 u Intelu (a potenciálně i AMD, tam uvidíme).

Je ale třeba říci, že reálně dostupné budou procesory s těmito jádry až za nějakou dobu, takže mezitím bude konkurence také dál. Nyní ARM v podstatě ještě jen ukazuje roadmapu a ačkoliv už nějací výrobci na vývoji křemíku pracují, na trh se mohou dostat třeba až za rok, ne-li třeba až v roce 2022. Například procesory Neoverse N1 teď teprve začínají být dostupné (Ampere Altra; Graviton2 byl k mání dřív, ale jen distančně přes cloud AWS).

ARM Neoverse N2: maximální efektivita

Druhá linie, tedy ta, která má zachovávat zaměření na vysokou efektivitu, byla do roadmapy přidána až nyní, pod kódovým označením Perseus (původně byl v oficiálním plánu jen Zeus). Jádro N2 bude asi podobnější N1, bude mít menší buffery (hloubky out-of-order front) a cache. Teoreticky také může jádro V1 mít více výpočetních jednotek (ALU, AGU, FPU) a vícestupňovou pipeline pro vyšší frekvence, než jádro N1, ale to je zatím nepotvrzené. Přesná schémata a údaje zatím ARM nedává.

N2 bude menší jádro co do těchto struktur (takže bude mít nižší IPC a možná i frekvence), ale díky tomu bude zabírat méně místa a mít nižší spotřebu. Výkon na jeden watt a na jeden milimetr čtvereční jádra bude tedy asi vyšší než u V1.

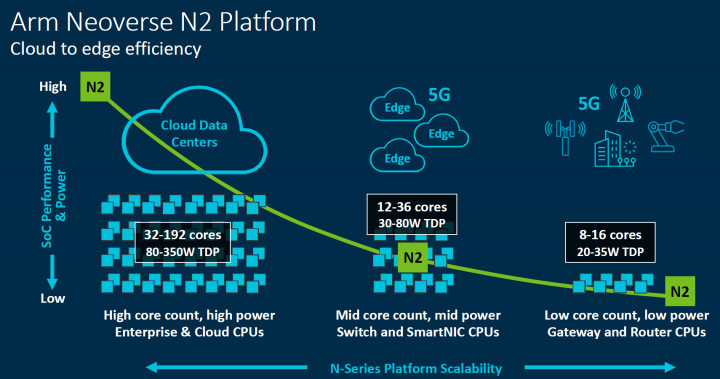

Podle ARMu typicky zákazníci asi budou s těmito jádry tvořit 128jádrové procesory, ale výkonnější prý mohou mít až 192 jader a TDP až 350 W. Takovéto maximální konfigurace mohou teoreticky mít i vyšší vícevláknový výkon než architektury Neoverse V1 díky tomu, že do určitého limitu TDP a plochy čipu nacpou výrazně více jader (ovšem samozřejmě je pak třeba, aby úlohy škálovaly, jinak výkon nemusí být lepší).

IPC má být až o 40 % vyšší než u Neoverse N1 (takže ne zas tak o moc nižší, kupodivu). Opět se ale bavíme o procesoru, který reálně může být k mání až za dva roky (a později než V1). V roadmapě je architektura N2 uvedená pro příští rok, ale fyzická dostupnost od klientů ARMu jako je Ampere/Amazon atd. bude zase asi trvat déle. Tyto procesory už také údajně mají být cíleny jen na 5nm proces, takže při srovnávání s dnešními 7nm to je třeba brát v potaz. Mají podporovat PCIe 5.0, DDR5, už i paměti HBM3 a CCIX 2.0 a nyní už i standard propojení CXL 2.0.

Jádro N2 není zřejmě sesterská architektura Neoverse V1, je vlastně o jednu generaci dál, základem má být asi příští ještě neodhalené jádro Cortex (A79?). I u tohoto jádra bude podpora SVE, ale bude méně výkonná. ARM využije variabilní šířky SVE a jednotky budou mít pořád šířku jen 128 bitů jako Neon. Pipeline budou stále dvě. Numerický SIMD výkon/propustnost tedy bude proti V1 poloviční na jeden cyklus.

Next-gen: Poseidon

Po této dvojici jader bude následovat další generace architektur, která má souhrnné označení Poseidon (jména jader ještě ARM nesděluje). V plánu je uvedení v roce 2022, ale skutečné čipy asi zase budou později než to. Tyto procesory mají opět přinášet minimálně 30% zlepšení výkonu a mají nastat i nějaká zlepšení ve výkonu SIMD a ve výpočtech umělé inteligence (patrně pomocí nějakých speciálních akcelerátorů/jednotek). Tyto procesory typicky budou 5nm nebo 3nm a počítá se u nich s podporou nových generací propojení CCIX a CXL a volitelně i s PCI Expressem 6.0.

Velké problémy pro Intel/AMD?

Cíle ARMu jsou hodně agresivní a slibné, takže je možné, že výrobci x86 procesorů už opravdu budou mít velké problémy. Zejména si AMD. Intel bude déle těžit ze zabetonovanosti svých pozic a dominantního postavení, ale AMD teprv dobývá zákazníky. A může se mu stát to, že když už se někdo odhodlá odpoutat od Xeonů, řekne si, že už rovnou může změnit i celou platformu.

Je nicméně třeba opět zopakovat, že tu srovnáváme procesory ARM, které byly oznámené, ale přijdou třeba až za dva roky, se současnými/minulými procesory Intel/AMD. Neoverse V1 už bude soupeřit se Saphire Rapids od Intelu nebo Epycem Milan s jádry Zen 3, ne-li už s Genoa/Zenem 4. A samozřejmě se pořád bavíme o výkonnostních slibech a očekáváních, kdežto v praxi to může vypadat trošku komplikovaněji.

Galerie: Prezentace serverových architektur ARM Neoverse V1 a ARM Neoverse N2

Zdroje: ServeTheHome, ARM