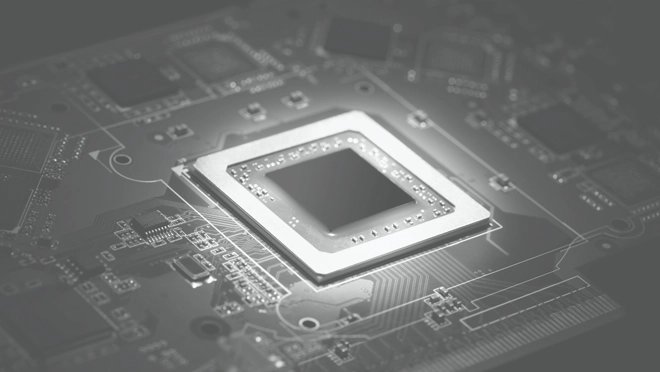

Jak se obecně předpokládalo už dříve, výpočetní jednotky Larrabee jsou vlastně x86 procesory vycházející z architektury procesoru Pentium, oproti kterému ale podporuje instrukce navíc, za zmínku stojí vektorová jednotka schopná pracovat až s 16 prvky a schopnost provozovat na každém jádře až čtyři vlákna zároveň. Každé má k dispozici vlastní L2 cache o velikosti 256 kB.

Intel ve svých materiálech hovoří o 8–48 jádrech v jednom čipu. Klasický grafický akcelerátor obsahuje mnoho jednotek s pevnou funkcí (fixed function), Larrabee je ale spíše mnohojádrové CPU optimalizované pro vysoce paralelizované výpočty. Komunikaci mezi jednotlivými jádry zajišťuje obousměrný ring-bus o šířce 1024 bitů, podobný ring-busu v čipu ATI R600 a jeho derivátech.

Pokud jste zdatní v angličtině a nechcete čekat na náš článek, mohu vás odkázat na rozbor na serveru Anandtech.