Po zrušení reformy instrukční sady x86 pod označením X86S koncem roku máme informace o dalším okleštění dříve plánovaných novinek, kterými chtěl Intel v budoucnu změnit tvář svých procesorů. Firma teď totiž zrušila plán na zavedení instrukcí AVX10 místo dnešních AVX-512. Tyto nové instrukce měly fungovat i na hybridních procesorech s jádry E-Core, ale obětovaly kvůli tomu 512bitovou šířku i kompatibilitu s AVX-512.

AVX10: Krok zpět z 512 bitů?

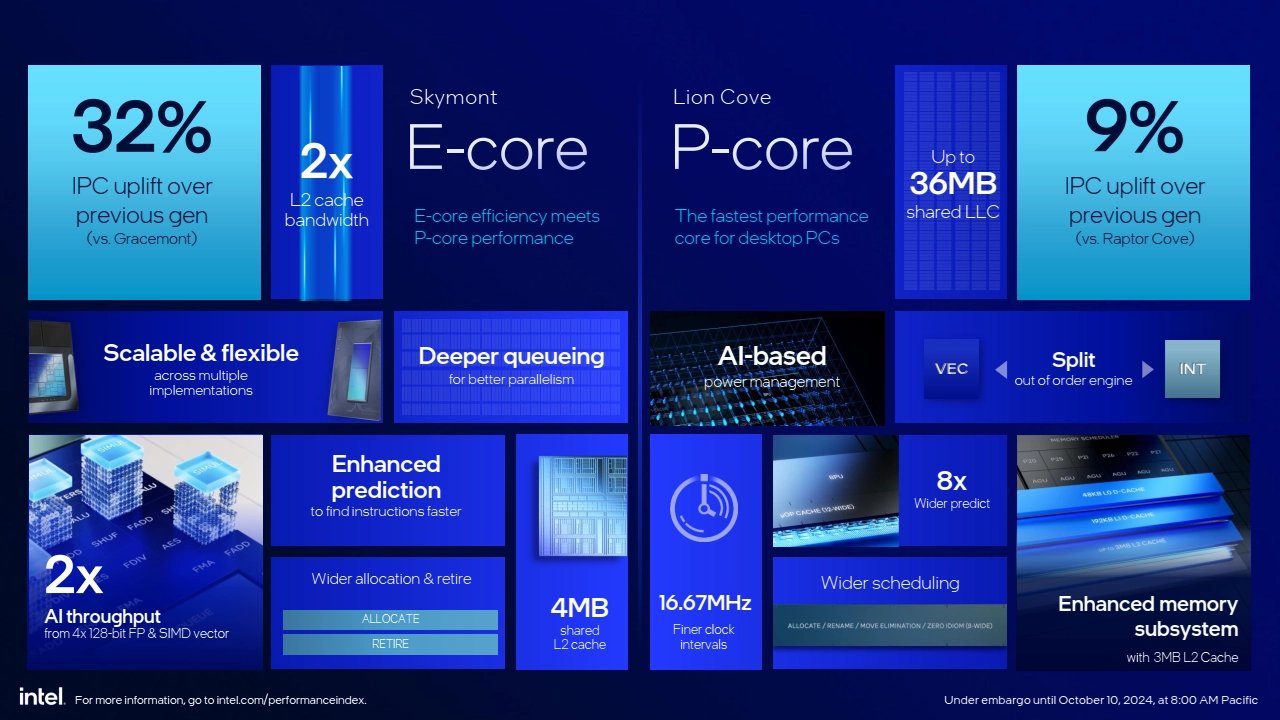

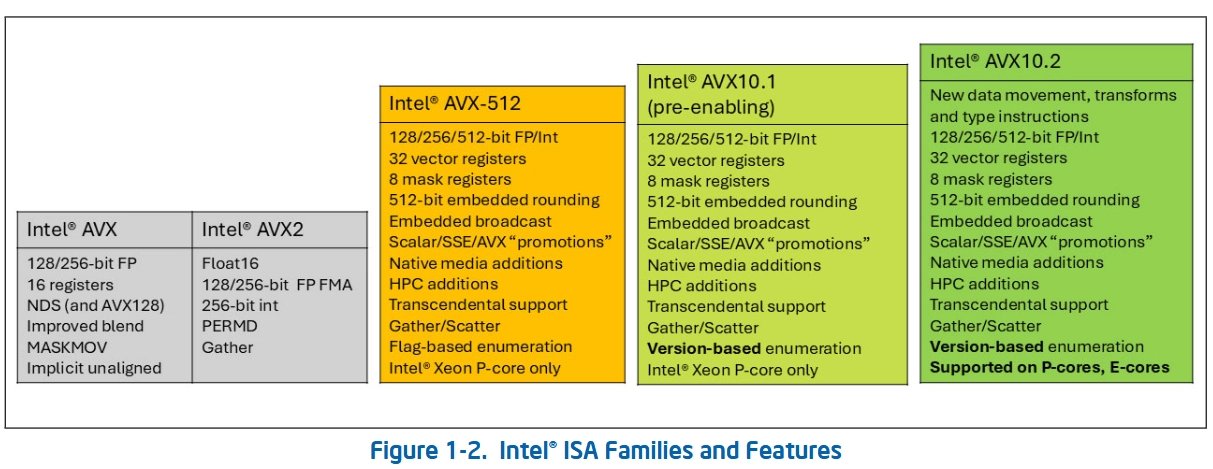

Intel představil AVX10 v létě 2023 a šlo o poměrně zajímavý krok. V té době měla firma problém s tím, že od Ice Lake a Tiger Lake sice její výkonná jádra („P-Core“) uměla i v procesorech pro PC 512bitové SIMD instrukce AVX-512, ale malá efektivní jádra E-Core i v posledních verzích Gracemont a Skymont umí jen 256bitové instrukce AVX2, takže na procesorech Alder Lake a novějších muselo být AVX-512 vypnuto.

Intel chtěl skrze AVX10 situaci řešit tak, že by z AVX-512 udělal 256bitové instrukce. 256bitové AVX10 by se dalo implementovat jen s registry YMM používanými pro AVX a AVX2 i v architekturách E-Core, ale přibyla by zlepšení v programovatelnosti a pružnosti, která přineslo AVX-512. V mnoha programech by stále mohl být značný přínos, ale bez potenciálu na dvojnásobný hrubý výpočetní výkon. AVX10 mělo mít i 512bitovou verzi, která by byla pokračováním plnohodnotného AVX-512, ale ta měla být jen volitelná, a hrozilo tak, že se dostane na vedlejší kolej. Intel asi 512bitovou verzi hodlal podporovat jen na procesorech Xeon a je otázka, zda by ji jednou třeba nezrušil.

Problém tohoto řešení byl, že všechen dosavadní software, který už někdo optimalizoval pro 512bitové instrukce AVX-512, by s novými procesory používajícími 256bitovou verzi nebyl kompatibilní, muselo by se zase začít od nuly. U nově psaného softwaru by si vývojáři museli vybírat, zda psát kód pro 512bitové procesory jako Zen 4 a Zen 5 (a jejich následníky) od AMD, nebo se soustředit na procesory Intelu s jen 256bitovými jednotkami. Pak by ale jejich software zase nebyl optimální pro výkonné serverové procesory Intel Xeon, u nichž měly 512bitové jednotky zůstat (a nevyužíval by ani potenciál jader AMD, samozřejmě).

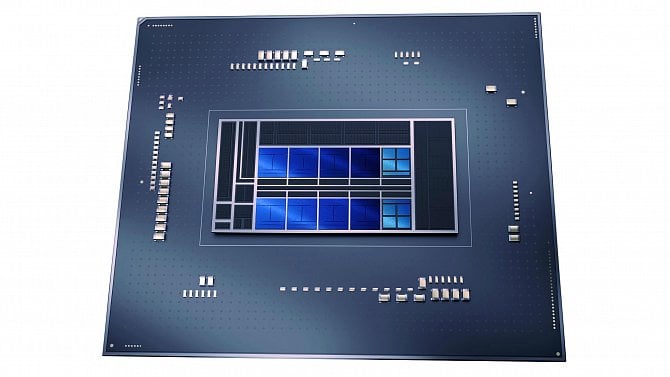

AVX10 v 512bitové formě, a tím i AVX-512, se v budoucnu dostane do jader P-Core i E-Core v procesorech Intel

Vyhrála kompatibilita, 256bitová omezená verze nebude

Tato razantní změna v přístupu k SIMD rozšířením v instrukční sadě x86 ale nakonec neproběhne. Intel teď vydal verzi 3.0 navrhované specifikace AVX10 a její hlavní novinka je, že návrh 256bitové verze těchto instrukcí byl zrušen – zatímco dříve byla 512bitová verze označovaná jako volitelný přídavek, nyní je opět hlavní a vlastně jedinou, ze specifikace naopak zmizely zmínky o možnosti mít pouze 256bitovou verzi AVX10 (pro pořádek je třeba říct, že zprvu Intel uvažoval ještě o tom, že bude povolená dokonce i jen 128bitová verze AVX10, ale tento nápad byl zatracen poměrně záhy).

Stále bude možné používat kratší jen 256bitové vektory tam, kde se to hodí (toto je možné zcela stejně už v rámci existujícího AVX-512), ale důležité je, že implementace v procesoru musí být vždy připravená i na plnotučné 512bitové. Intel tuto změnu a zrušení koncepce pouze 256bitové verze AVX10 potvrdil i v patchích, které byly zaslány do překladače GCC.

Toto pravděpodobně znamená, že firma změní plány a její budoucí procesorová jádra E-Core dostanou plnou podporu 512bitových SIMD instrukcí AVX-512, která jim teď chybí – ne nutně s plným výkonem, ale s plnou kompatibilitou se všemi 512bitovými operacemi, takže už je konečně bude moci podporovat i jádro P-Core v hybridních procesorech. AVX-512 se tedy vrátí do klientských CPU Intelu a konečně budou tyto operace dostupné na všech relevantních nových CPU (jelikož je od generace Zen 4 umí i procesory AMD).

Nově definované instrukce AVX10. Původně byly přípustné procesory podporující pouze 256bitovou verzi, to je zrušeno. Všechny procesory s AVX10 budou muset podporovat 512bitové operace, a tedy také být kompatibilní s kódem používajícím AVX-512

Cílem 256bitové verze instrukcí AVX10 bylo podle všeho, aby implementace plnotučné podpory AVX-512 nenavyšovala plochu jader E-Core. Jádro Zen 4 od AMD nicméně ukázalo alternativní cestu, že je možné vytvořit poměrně efektivní implementaci plně 512bitových instrukcí AVX-512 i s 256bitovými výpočetními jednotkami a omezeným množstvím plně 512bitového hardwaru (například shuffle jednotek a samotných registrů ZMM). Sice u něj asi ona daň v počtu tranzistorů a ploše je, ale docela podstatné je, že s ní není spojena daň zvýšené spotřeby. A taková implementace má větší výkonnostní potenciál než čistě 256bitové instrukční rozšíření. Intel se tedy pravděpodobně rozhodl jít stejnou cestou.

Toto rozhodnutí a zrušení plánů na procesory s jen 256bitovým AVX10 je ale přínosné hlavně díky tomu, že nevznikne onen výše popisovaný dlouhodobý problém s kompatibilitou. Zde tedy Intel chválíme, že nakonec zvolil lepší variantu, i když to znamenalo ustoupit ze svých původních záměrů.

Samotné rozšíření AVX10 zůstává stále v plánech Intelu (a v této verzi, kdy je vždy plně 512bitové, ho asi přijme i AMD). Ale bude z něj teď pouze lineární evoluce AVX-512 bez odboček a rozvětvování. Na procesorech s AVX10 by po tomto přehodnocení automaticky měl fungovat všechen dosavadní software používající instrukce AVX-512, zatímco na zamýšlené omezené 256bitové verzi by nefungoval.

Je třeba říct, že osekaná 256bitová verze (a to, že se z 512bitové stala volitelná věc) představovala v AVX10 největší novinku a v podstatě drtivou většinu změn. Takže po jejím eliminování toho AVX10 nebude přinášet mnoho nového proti AVX-512. Bude asi hlavně kosmetickou a „uklízecí“ úpravou (či „rebase“ momentem), která například převede jednotlivá rozšíření AVX-512, která jsou dnes teoreticky samostatná a software musí jejich podporu jednotlivě detekovat pomocí flagů, na systém definovaných verzí, kdy určité číslo verze (například AVX10.2) bude obsahovat určité dřívější subsety a následující verze bude také garantovat jejich přítomnost, takže by se vývojáři měli v rozšířeních lépe vyznat.

Ukázka harmonizace vývoje mezi AMD a Intelem?

Toto je možná výsledek spolupráce AMD s Intelem v rámci x86 Ecosystem Advisory Group, což je loni založené konsorcium, kde Intel spolu s AMD a dalšími zainteresovanými partnery chtějí harmonizovat právě takovéto aspekty procesorů x86, aby se mezi řešeními obou firem zlepšila kompatibilita a tím i atraktivnost celé platformy.

x86 Ecosystem Advisory Group má předcházet podobným incidentům, kdy by budoucí plány obou firem divergovaly jako zde u AVX-512 a AVX10. Je dost možné, že opuštění 256bitové varianty AVX10 bylo dohodnuto právě v tomto „orgánu“.