V červnu odhalilo AMD technologii 3D V-Cache, jedno z prvních řešení používající v procesorech vrstvení čipletů (pravda, Intel Lakefield byl na světě dříve). Tato novinka přináší do procesorů s architekturou Zen 3 výrazně rozšířenou L3 cache, která má vylepšit výkon této architektury. Včera AMD oznámilo první procesory, které budou tuto vrstvenou cache mít: superpočítačové Epycy Milan-X. Už víme, kdy se 3D V-cache začne prodávat.

3D V-Cache jde do praxe

Jak jméno naznačuje, je Milan-X rozšíření již vydaného a prodávaného Epycu 7003 „Milan“, jenž má až 64 jader Zen 3. Procesory Milan-X používají stejný IO čiplet, ale na CPU čipletech je vždy navíc pomocí technologie Direct Bonding a TSV připojený dodatečný 7nm křemík o rozměru zhruba 6 × 6 mm, který přidává kapacitu L3 cache, jež se tímto ztrojnásobuje.

Procesory Milan-X tak dokáží držet v mezipaměti mnohem více dat, díky čemuž se efektivně snižuje průměrná latence RAM, protože více požadavků na data se podaří obsloužit z L3 cache. Mohlo by to fungovat podobně jako GPU s architekturou RDNA 2, které díky velké Infinity Cache mají výkon, jako by disponovaly výrazně vyšší propustnost pamětí.

Samotná L3 cache má zřejmě s přidanou kapacitou o něco vyšší latenci (snad asi o 10 %, což by bylo cca 5 cyklů), což ale při zvyšování kapacity nastává i normálně v případě, kdy cache je v jednom kusu křemíku pohromadě. Ale právě díky vyšší kapacitě (hit-rate) by měla 96MB L3 snížit celkové latence při přístupu k datům z RAM.

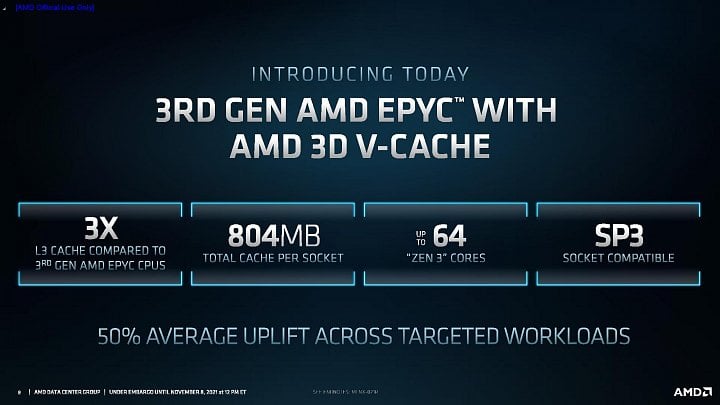

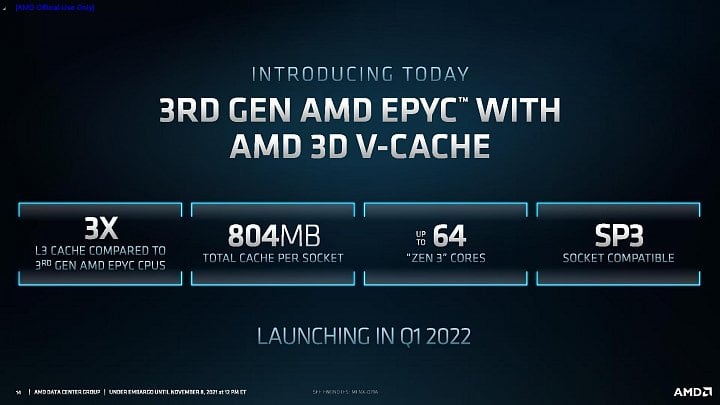

AMD ještě neodhalilo přímo konkrétní modely procesorů Epyc Milan-X, ale sdělilo rámcové parametry. CPU budou mít až 64 jader Zen 3, přičemž by měla fungovat ve stejných deskách jako běžné Epycy 7003, jen bude asi třeba aktualizovat fimrware. Nový procesor je kompatibilní se socketem SP3 a má stejnou konektivitu (128 linek PCI Express 4.0, osmikanálový řadič DDR4–3200). Zatímco Milan má ale 256 MB L3 cache (8 × 32 MB), pro Milan-X uvádí AMD, že jednom socketu/procesoru je 768 MB L3 cache. Každý z osmi CCX/CPU čipletů, z nichž se procesor skládá, má tedy 96 MB L3 cache. AMD ve slajdech uvádí až 804 MB cache, to je však součet celkem 4 MB v L1 jednotlivých cache, 32 MB v L2 cache jader a konečně 768 MB L3 (v 8 blocích po 96 MB) cache v 64jádrovém procesoru.

Více: AMD odhalilo technologii 3D čipletů: Procesory s 64MB 3D V-Cache osazenou nad jádra Zen 3

Více o 3D V-Cache bylo již sděleno v létě. AMD nyní opět zopakovalo, že je použitá technologie Direct Bonding, kde jsou propojené měděné vodiče v TSV přímo s měděnými vodiči kovových vrstev procesoru a čipletu s cache, aniž by mezi křemíky byly kuličky pájky („microbumps“). Například křemíkové interposery a technologie Intel EMIB a Foveros v současné verzi používají pájky, což ale má horší vlastnosti.

Podle AMD odkáže Direct Bonding mít až 15× vyšší hustotu kontaktů. Proti propojení přes obyčejný substrát (tedy stylem, jak jsou nyní propojené CPU čiplety a IO čiplety v procesorech AMD) je hustota dokonce až 200× lepší. Ještě důležitější možná je, že má také být lepší energetická efektivita. Proti řešení s pájkou potřebuje propojení měď–měď méně energie, má být víc než 3× více energeticky efektivní.

Výrazné zrychlení pro simulace, HPC, technické aplikace

AMD zatím neřeklo, zda procesory budou mít zachováno stejné TDP, ale L3 cache navíc má zlepšovat výkon, a v některých případech i hodně. Tam, kde je paměťový výkon a množství dat, které se vejde do cache největším omezením, by Milan-X mohl přinášet velká zlepšení.

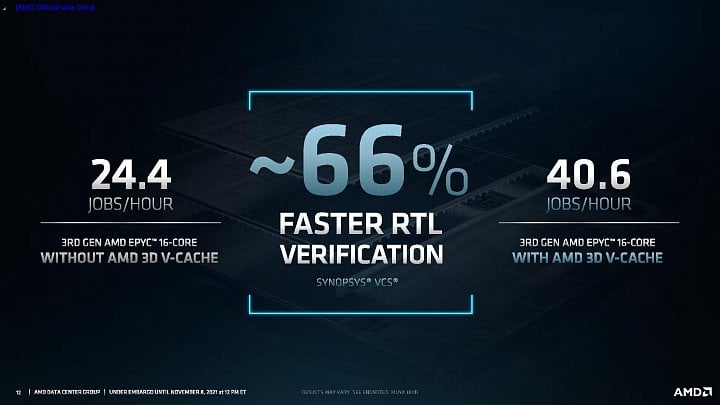

Hodně by se mohl vyplácet v HPC (vědeckých výpočtech), ale AMD uvádí jako další příklady například práci s EDA nástroji Synopsys při vývoji čipů, kde má Milan-X zlepšit výkon o 66 %.

Nárůsty výkonu asi vůbec nebudou obecně pozorovatelné ve všech úlohách, ve velkém množství úloh, ne-li ve většině, nemusí být rozdíl vůbec velký. Možná se najdou i případy žádného nebo negativního zrychlení kvůli tomu, že cache ubere část z přídělu TDP a zhoršila se latence L3. Proto také AMD určitě bude dál prodávat i běžnou verzi Epyců 7003 Milan bez této cache navíc. Milan-X lze asi vnímat jako specializované řešení.

Tip: Unikly parametry prvních procesorů AMD s 3D V-Cache: Milan-X se 768 MB L3 cache

Vydání v první čtvrtině roku 2022

Podle AMD by tyto procesory měly být reálně dostupné zákazníkům v prvním kvartále roku 2022, nyní jsou zatím k dispozici vzorky. Ty jsou k dispozici k testování v cloudu Azure, kde Microsoft nabízí instance HBv3 s procesory Milan-X. Ty jsou asi první možnost jak si výkon Zenu 3 s 3D V-Cache vyzkoušet.

Microsoft také zveřejnil blogpost s benchmarky, které si můžete v případě zájmu prostudovat.

Podle neoficiálních zdrojů se výroba CPU čipletů osazenou 3D V-Cache rozjela nebo rozjede v sériovém měřítku tento měsíc, takže je logické, že do obchodů přijdou finální procesory až o pár měsíců později. Snad je určitá naděje, že spotřebitelská verze, tedy procesory Ryzen 5000 nebo Ryzen 6000 s těmito CPU čiplety nastavenými o L3 cache, bude na trhu o něco dřív, třeba už začátkem Q1 2022. Při vydávání procesorů pro PC totiž AMD bývá agresivnější. Firma je ale zatím neohlásila, protože včerejší akce se týkala jenom serverů.

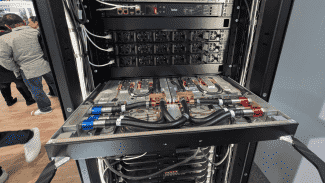

Galerie: Procesory AMD Epyc Milan-X s 3D V-Cache

Zdroje: AMD, Tom's Hardware, AnandTech