Po Intelu teď odprezentovalo své novinky na Computexu 2021 AMD. Jsou mezi nimi APU Ryzen 5000G, grafiky Radeon RX 6000M pro notebooky a upscaling FSR míněný jako konkurence proti DLSS od Nvidie. Vůbec nejzajímavější ale byla novinka procesorová: 3D čiplety s křemíky navrstvenými na sobě zřejmě přicházejí do procesorů Ryzen.

3D čiplety na Zenu 3

První procesorová novinka na Computexu se týkala desktopových APU, ale s dovolení se na ni podíváme až v dalším článku. Druhá procesorová novinka je totiž o hodně překvapivější a o hodně zajímavější. V samém závěru prezentace šéfka AMD Lisa Su coby takovou třešničku na dortu odhalila technologii procesorů s 3D pouzdřením aktivních čipletů. To je něco, co v desktopovém CPU zatím nebylo.

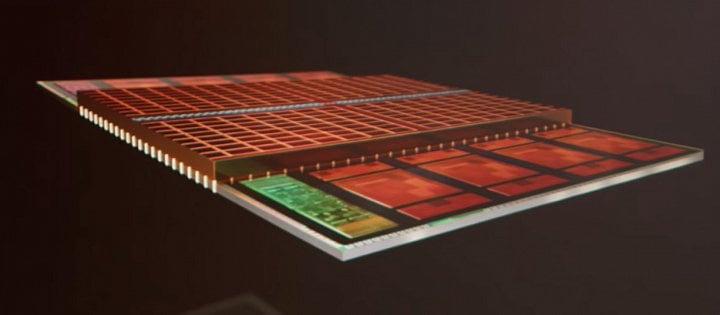

3D aktivní čiplety znamenají, že jsou dva aktivní křemíky položené na sebe a propojené kontakty. Su odhalila, že AMD (zřejmě v partnerství s TSMC, jde zřejmě o jeho postup Chip-on-Wafer) vyvinulo technologii, která mu dovolí takto osadit druhý čip na horní stranu CPU čipletu v procesorech Epyc nebo Ryzen. A co víc, dokonce už ji údajně i úspěšně demonstrovali.

Má to dokonce fungovat s čiplety Ryzenů 5000, které zřejmě s technologií už v návrhu počítají, protože Lisa Su ukazovala prototyp, který je tvořený Ryzenem 9 5900X s přidaným čipletem. Delidovaný exemplář, který můžete vidět na snímcích z videa, má druhou vrstvu křemíku nasazenou jen na pravý ze svých CPU čipletů pro možnost srovnání, ale funkční prototyp má samozřejmě obě (a je to vše zakryté a chráněné rozvaděčem tepla). Jak spodní, tak vrchní křemík jsou ztenčené, aby se vešly pod stejný rozvaděč tepla a na stejný substrát, jako se používá standardně.

3D Vertical Cache

Rolí druhé vrstvy křemíku je v této fázi technologie přidání L3 cache navíc, tzv. 3D Vertical Cache (3D V-Cache). Jde o čip tvořený pamětí SRAM a nějakou komunikační logikou pro obsluhu, který je nasazen na CPU čiplet. Ten musí být na začátku provrtán kanálky (tzv. TSV) s vodivou cestou, protože obvody CPU čipletu jsou na jeho spodní straně. Na tyto kanálky jsou napojené kontakty druhého přidaného křemíku a vše je slepeno.

Druhý čiplet přidává 64 MB cache jednomu CPU čipletu (s osmi jádry), takže jednočipletový procesor by měl 96 MB L3 cache (64 MB plus již přítomných 32 MB), ale model s 12 nebo 16 jádry už 192 MB (2 × 96 MB, předpokládáme). Propustnost do této cache je údajně 2 TB/s a tato technologie má prý také nejlepší energetickou efektivitu na světě, nepoužívá vůbec kuličky pájky a místo toho jsou přímo spojené měděné vodiče, což má údajně zlepšit energetickou efektivitu spoje trojnásobně proti konkurenčním technologiím.

Čip s cache navíc je údajně také 7nm a má plochu cca 6 × 6 mm (36 mm²). To je zajímavé, protože má zdá se vyšší hustotu než L3 cache na CPU čipletech. Pravděpodobně je vyroben s knihovnami o vyšší hustotě. Docela by nás zajímalo, zda SRAM na tomto čipu dosahuje stejného výkonu a jak je to s latencí. Asi by nebylo zvláštní, pokud by bloky na sekundárním čipu měly vyšší latenci než lokálně přítomná část cache. Ale AMD tuto přídavnou kapacitu neoznačuje jako L4, nýbrž jako L3 cache, což implikuje, že je na stejné úrovni jako integrovaný 32MB blok mezipaměti.

Obří cache pomáhá ve hrách

Vzorky snad již existují, AMD ukazovalo na videu nahrané demo 3D V-cache ve hře Gears 5. Na videu byly porovnané dva dvanáctijádrové Ryzeny 5900X na stejném taktu (pevně nastavených 4,0 GHz), z nichž jeden měl 192MB 3D V-Cache a v průměru dosahoval o 12 % lepší snímkové frekvence. V dalších hrách byla nárůsty dokonce i vyšší (v Monster Hunter World pod DX11 +25 %), takže v průměru to prý vychází na asi 15% zlepšení FPS ve hrách.

Tato technologie by tedy dokázala zlepšit výkon ve hrách, dost možná by dokonce mohla být odpovědí na pokroky v IPC, které slibuje Alder Lake (s prý až o 20 % zlepšeným jednovláknovým výkonem) od Intelu.

Budou i v Ryzenech?

Nevíme ale, zda se proti Alder Lake tato technologie postaví, zatím jde jen o prototyp. AMD uvádí, že podle jeho plánu bude firma připravená rozjet výrobu takovýchto procesorů do konce letošního roku. To znamená, že uvedení na trh určitě může být nejdříve v roce 2022, a to třeba až několik měsíců po jeho začátku. Ačkoliv tedy čiplety Zen 3 jsou podle všeho připravené k prošpikování TSV cestami (zajímavý poznatek, toto muselo trošku zhoršit hustotu tranzistorů) a k osazení 3D V-cache, během jejich života k tomu vůbec nemusí dojít. AMD by toto mohlo komerčně nasadit až později třeba u Ryzenů 7000, 8000…

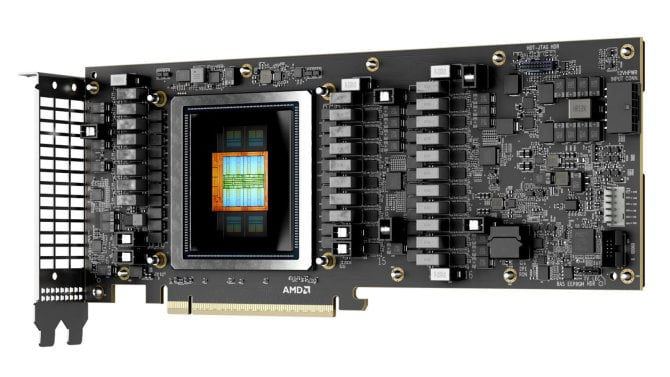

… nebo také vůbec. Jak to u pokročilých technologií chodí, legrácky jako HBM2, křemíkové interposery a možná i toto jsou často tak nákladné, že se objeví jen u enterprise a serverových produktů. Podle informačních úniků AMD určitě chystá verzi procesorů Epyc 7003 s takto rozšířenou cache (64jádrový model by měl celkem 768 MB L3 cache, 8 × 96 MB!), která má označení Milan-X. Ta se tedy příští rok asi určitě objeví v rukou nějakých movitých uživatelů, možná v superpočítačích. Zda se dostane i na Ryzen, už tak jasné není. Později má asi existovat i takováto verze procesorů s jádry Zen 4, Epyc „Genoa-X“.

Existuje asi naděje v tom, pokud by se 3D V-Cache osazovala na CPU čiplety předtím, než by se osadily na pouzdro celého CPU. Pak by už nebylo tak drahé jich část odklonit do vybraných luxusních verzí Ryzenů 5000 (nebo 6000 a tak dále). Ale raději bych se na to teď neupínal. Byla by to vysoce zajímavá CPU, pokud by to klaplo, ale trošku se bojím, aby to nebyly naděje z kategorie „příliš dobré, než aby to mohla být pravda“, byť si teď AMD Ryzen vybralo pro demo. Může jít jen o tom, že na malém AM4 procesoru s jedním nebo dvěma čiplety se experimentuje lépe. Budeme ovšem napjatě sledovat úniky informací, zda se přece jen štěstí na sprosté PC lidi neusměje.

Myslíte si, že se 3D V-cache dostane i do procesorů AMD Ryzen pro běžná desktop PC nebo notebooky?

Pozor na chlazení… a cenu

Tato technologie má docela velké možnosti, zvlášť pokud by se druhý obvod neomezil jenom na cache, nebo pokud by by jich bylo výhledově možné osadit na sebe i víc. Druhá vrstva by mohla být i logická a hrát funkcionalitu čipsetu – toto již má Intel pomocí technologie Foveros v procesorech Lakefield, kde je ale CPU čiplet na horní straně a čipsetový čiplet vespod. Jde o trošku odlišné technologie, ale asi se dá říct, že Intel byl první, byť zatím toto vrstvení nevyužil v moc zajímavém produktu (což ovšem asi byla chyba nekvalitního 10nm procesu – další dějství budou u 7nm Meteor Lake, kde by to mohla být jiná písnička).

Nicméně u AMD jde o překvapení, firma zatím u procesorů upřednostňovala levné běžné techniky pouzdření, místo aby třeba u Epyců použila křemíkový interposer ke zlepšení výkonu a energetické efektivity. Foveros také prý používá na kontakty pájku, což jak bylo řečeno má údajně být méně efektivní (hustota je nižší a komunikace spotřebuje více energie) než technologie Chip-on-Wafer od TSMC, kterou použije AMD.

Slabina je jednak cena – toto nebude nijak levné, takže pokud si brousíte zuby, raději kroťte očekávání, protože je dost možné, že až věc přijde na trh, nepřijde vám cenově zajímavá. Druhý problém je spotřeba – lépe řečeno, chlazení. Čiplet na horní straně, i pokud by měl sám nízkou spotřebu, pravděpodobně zhoršuje chlazení spodního čipletu, který v případě 3D Vertical Cache asi bude tvořit většinu tepla. Při odvodu do rozvaděče tepla a chladiče bude teplo nejprv muset přejít přes nalepený druhý čiplet, což asi zpomalí jeho odchod a se stejným chladičem bude teplota CPU čipletu ve výsledku horší. Malé čiplety v Ryzenech se přitom už tak chladí spíše špatně kvůli ploše, takže zde nastane možná ještě dílčí zhoršení navíc.

Aktualizováno (2. 6. 2021): nové detaily, Ryzeny X3D vypadají reálněji

AMD už odpovědělo na některé dotazy novinářů a jak se příslovečný prach po včerejší prezentaci usadil, máme o této technologii jasnější obrázek.

Bylo potvrzeno, že horní čiplet s L3 cache je vyřáběný na 7nm procesu, ale do 36 mm² dostane dvojnásobek L3 cache, zatímco 32 MB přímo v hlavním CPU čipletu zabere 27 mm². Je to z části proto, že cache čiplet používá knihovny optimalizované na hustotu SRAM, které dokáží cache smrsknout na výrazně menší prostor. Zároveň ale CPU čiplet obsahuje v cache struktury, již připravené na přistavění dalšího patra cache, jako tagy a snoop filtery. AMD počítalo s tímto řešením od začátku, prostor pro TSV cesty v CPU čipletech je ve všech vyrobených CPU čipletech pro Ryzeny 5000 (dokonce si už někdo všiml, že v jedné staré prezentaci AMD uvádělo L3 cache s kapacitou 32 MB+, což dost možná počítalo s tímto 3D rozšířením)…

https://twitter.com/aschilling/status/1399664821717569542

Přídavná cache je na stejné úrovni jako integrovaná L3 cache, nejde tedy o L4. Z pohledu softwaru bude transparentní a data se budou rozkládat mezi bloky v základní části a nastavěné části L3 cache. Má to obnášet jen mírné přidání spotřeby navíc a lehké zvýšení latence L3 cache.

Velikost čipletu s 3D V-Cache je zhruba taková, že překryje jen plochu L3 cache umístěnou v prostředku CPU čipletu. To je důležité pro chlazení, protože bloky L3 cache neprodukují tolik tepla. Krajní části CPU v čipletu s jádry, které se hřejí, při aplikaci L3 cache dostanou separátní překryv z destičky křemíku, jejímž účelem je jen vést teplo do chladiče nad celým štosem. CPU čiplet musí být kvůli vytvoření TSV kontaktů skrz křemík snížen a jak L3 cache v druhém čipletu, tak tyto křemíkové vložky vyplňují takto ušetřený prostor. Díky tomu není celek tlustší, než původní jednoduchý CPU čiplet, takže se vše vejde do standardního pouzdra, pod standardní rozvaděč tepla a pod standardní chladič. To, že je přes přidání křemíkové vložky výška hmoty nad aktivní spodní stranou CPU čipletu stejná, by právě měla dovolovat, aby se chlazení (snad) moc neztížilo.

3D V-Cache i v Ryzenech

Nejpodstatnější zpráva: Ian Cutress z AnandTechu i další novináři potvrdili, že tato technologie se dostane do procesorů Ryzen, tedy můžeme poopravit původní skepticismus. Údajně se na trh Ryzeny s 3D V-Cache dostanou ještě v generaci Zen 3, tedy možná jako Ryzen 5000 (nebo Ryzen 6000). Mělo by to být příští rok, pokud se výroba rozběhne koncem letoška, snad by mohlo něco vyjít v Q1 nebo Q2 2022.

https://twitter.com/IanCutress/status/1399766139769602058

Ovšem pozor, pořád platí, že takové Ryzeny by byly drahé. AMD uvádí, že by se technologie měla dostat do highendových modelů, takže klidně může dojít na to, že tento bonus dostane jen 16jádro, které již i bez toho stojí 800 $ a pro většinu uživatelů není výhodné. 3D verze by měla nejspíš stát ještě víc, takže by pak z tohoto procesoru asi byla technologicky moc atraktivní věc, ale pro většinu zákazníků to vůbec nemusí hrát roli. Nepůjde tedy asi ani o odpověď na Alder Lake, protože většina nabídky Ryzenů, která bude těmto CPU čelit, nejspíš toto vylepšení nedostane.

Víc vrstev cache je prý také možných

AMD jinak potvrdilo, že L3 cache v přidaném 3D čipletu má jen jednu vrstvu, ale technologie TSMC počítá s tím, že by i přes tuto vrstvu mohly být provrtané TSV a nad ní by mohly být nastavené ještě další vrstvy. Není jasné, zda se toto dostane na trh, ale podle leakera ExecutableFix, který toto celé dopředu předpověděl (tweetem o lasagních), prý je možné osadit až osm vrstev cache. Tolik asi v první generaci nemusí být použito, ale Epyc Milan-X, o němž kolují zvěsti, byť ho AMD ještě nepotvrdilo, by tedy mohl mít ještě víc cache, než jsme si mysleli. Pokud by AMD nasadilo dvě vrstvy, bylo by to 1 GB přidané kapacity L3 cache, se čtyřmi 2 GB…