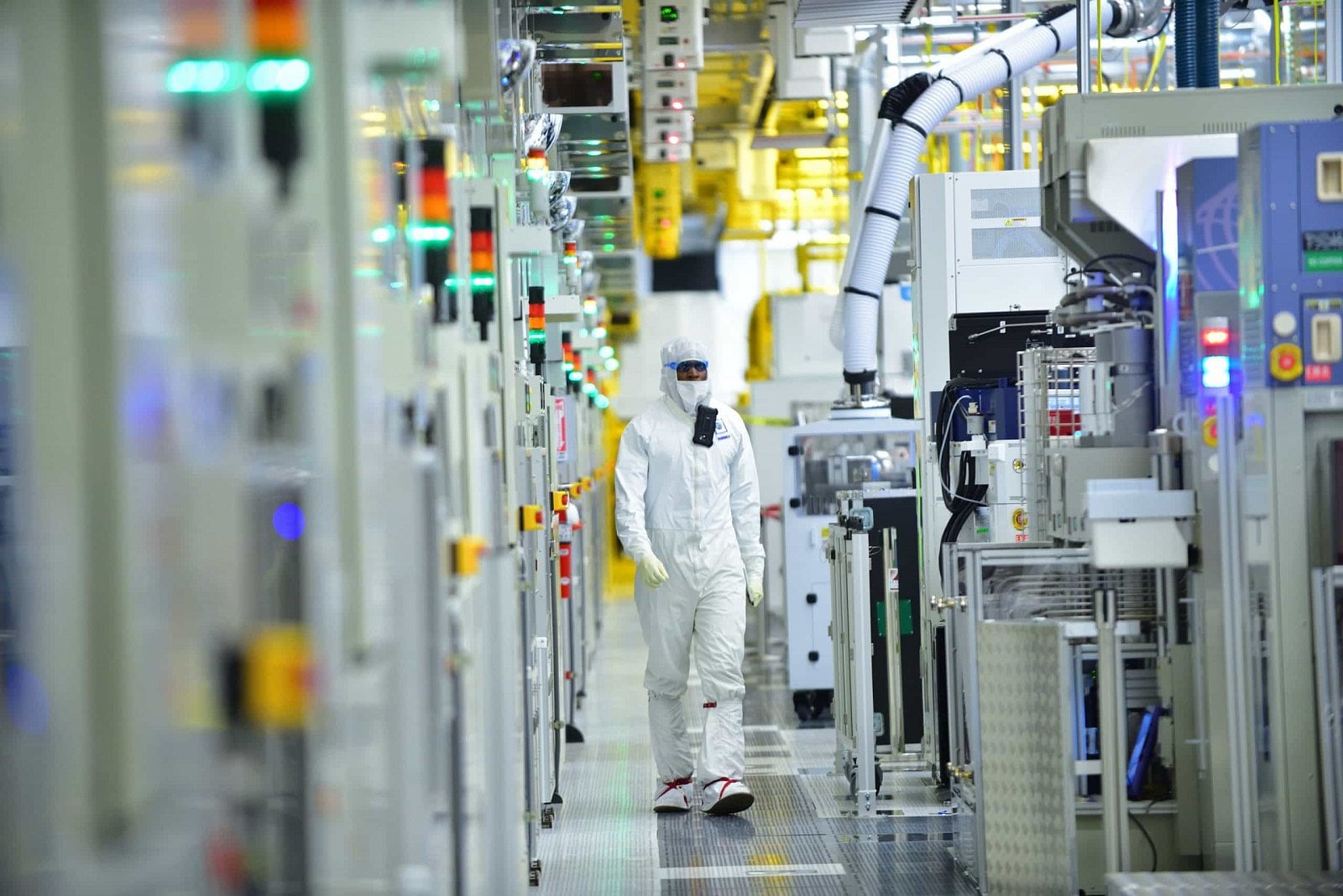

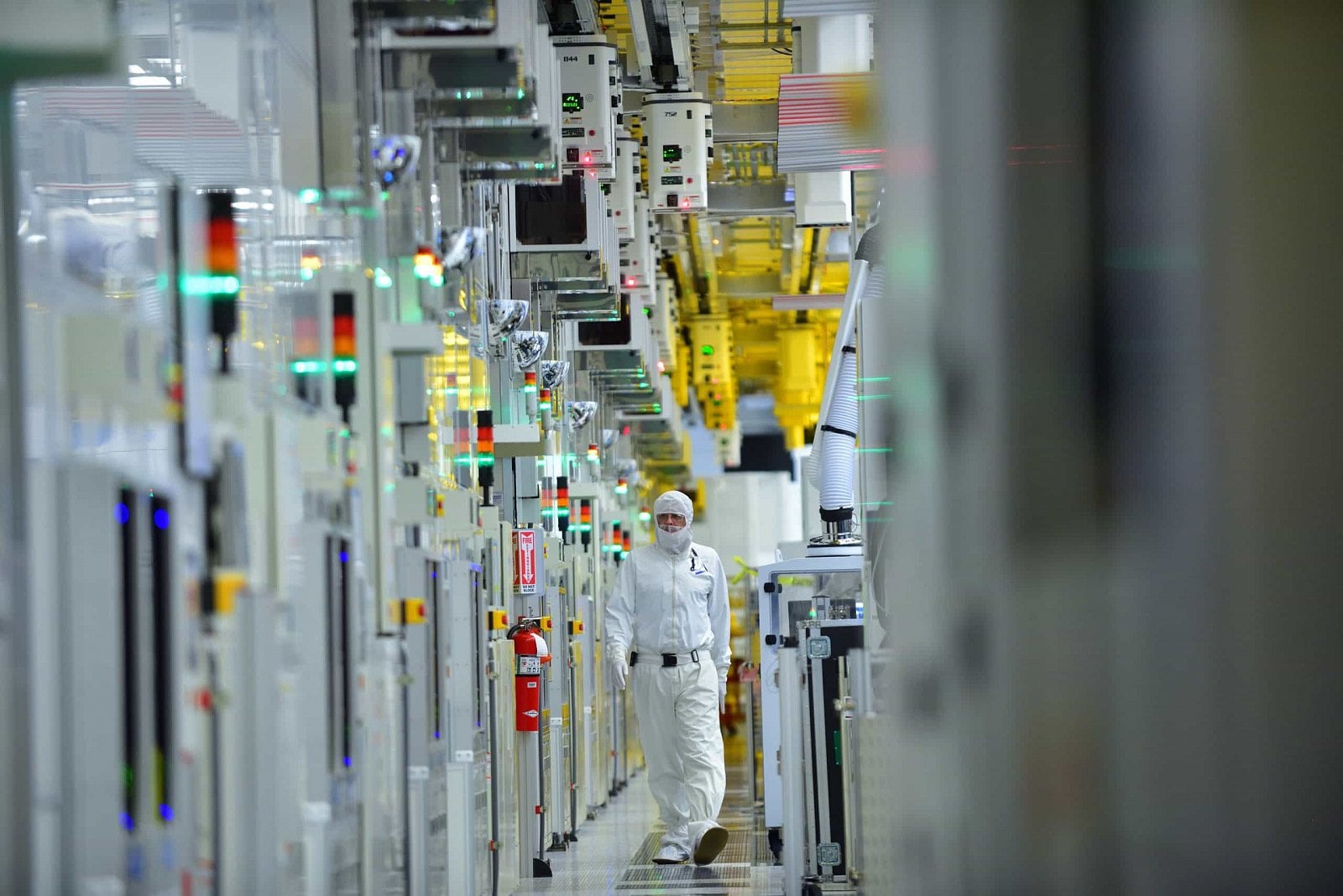

Před pár dny jsme tu psali, kterak Samsung připravuje 6nm výrobní proces jako jakýsi mezikrok mezi 7nm a 5nm generací. Podobný proces bude mít také TSMC. Také tento křemíkový lídr dneška (minimálně do doby, než Intel uvede 10nm čipy, mu tak lze asi říct úplně bezpečně) totiž oznámil výrobní proces, označený jako 6nm.

Tato technologie má označení CLN6FF (nebo zkráceně N6) a jak už jméno indikuje, jde o evoluci 7nm procesu N7 (CLN7FF), používající stále tranzistory typu FinFET. Na rozdíl od 5nm procesu, na kterém má začít výroba příští rok, ale nejde úplně o přechod na novou generaci. 7nm proces má vesměs stále používat technologii a postupy vytvořené pro 7nm proces, jen dále vyladěné. Návrháři čipů proto budou moci použít stejnou metodologii a nástroje, takže portování návrhu na tento proces by mělo být hodně usnadněno.

6nm proces by už podle oznámení měl obsahovat technologii EUV, takže bude vlastně evolucí už druhé generace 7nm výroby („N7+“), ne té prvotní, která se rozjela už loni a která ještě EUV nepoužívá. Podle TSMC toto plus další zlepšení umožňují dosáhnout až o 18 % vyšší hustoty tranzistorů v logických obvodech. Toto srovnání vlastností je ale spočítáno proti první ne-EUV generaci 7nm procesu, na což je třeba dát pozor. Proti N7+ by asi zvětšení hustoty mohlo být mnohem menší, možná jen nějaké jednotky procent. I N7+ totiž má značně zlepšovat hustotu (starší informace dokonce uváděly, že o 20 % proti N7 – to ale nemusí znamenat, že by proces byl hustější než N6, spíš se mezitím detaily změnily nebo nejde o přímo srovnatelné údaje).

Proces by asi také mohl dosahovat vyšší výkon (frekvennce) při stejné spotřebě, anebo zase nižší spotřebu při stejné frekvenci, ale tyto údaje TSMC už nesdělilo. Podle tiskové zprávy má N6 přinést výhody ve výkonu i v ceně. Zlevnění by ovšem mohlo spočívat v tom, že se sníží plocha čipů a vejde se jich víc na eden wafer, ne přímo v ceně za vyrobení jedné křemíkové desky.

6 nm přijde až po 5nm technologii, jako levnější alternativa

Tento proces se do akce asi dostane až za nějakou dobu. TSMC uvádí, že „risk production,“ tedy zkušební fáze před normální masovou výrobou, má započít až v první čtvrtině roku 2020. Risk production na 5nm procesu už přitom měla odstartovat tento měsíc. To znamená, že 6nm technologie přijde později, možná skoro rok po 5nm čipech. Nepůjde tedy o evoluční mezičlánek nebo mezikrok v chronologickém smyslu. Spíš bude 6nm proces jakýmsi doplňkem pro 5nm technologii. Poté, co přijde 5 nm do výroby, bude tento proces poměrně drahý. Čipy více hledící na cenu, které předtím třeba používaly jen 10nm nebo 16nm/14nm/12nm technologii místo 7 nm, tedy na 5 nm hned nepřejdou. Pro podobné produkty – jako například mobilní SoC do mainstreamových a lowendových telefonů – by ale právě 6nm proces mohl v 5nm éře představovat dostupnější alternativu, byť s ne tak vysokým výkonem a efektivitou. Mezičlánek mez 7 a 5 nm to tedy bude spíše z hlediska nákladů.

Pokud platí risk production v první polovině roku 2020, pak se ale asi 6nm čipy v telefonech objeví až v roce 2021. Od fáze risk production je ještě poměrně dlouhá doba, takže dané čipy SoC by mohly vyjít dejme tomu koncem roku a zařízení s nimi pak po Vánocích v roce dalším. V grafických procesorech GeForce a Radeon se 6nm technologie možná nemusí objevit. Tato sféra by se ze 7nm mohla překlopit rovnou na 5 nm. Na druhou stranu v případě 12nm půlgenerace k nasazení v GPU došlo, takže vyloučené nejsou ani 6nm grafiky.