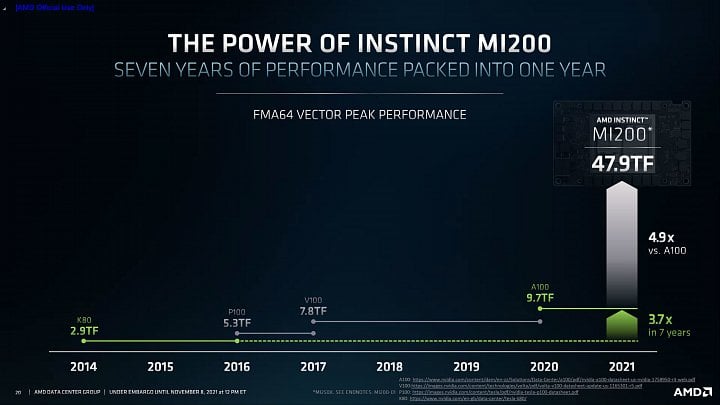

AMD tento týden představovalo novinky nebo plány pro serverový trh a oblast HPC. Vedle procesorů Milan-X s 3D V-Cache, serverové roadmapy Zenu 4/4c a 6nm GPU Instinct MI200 stojí vypíchnout ještě jednu věc.

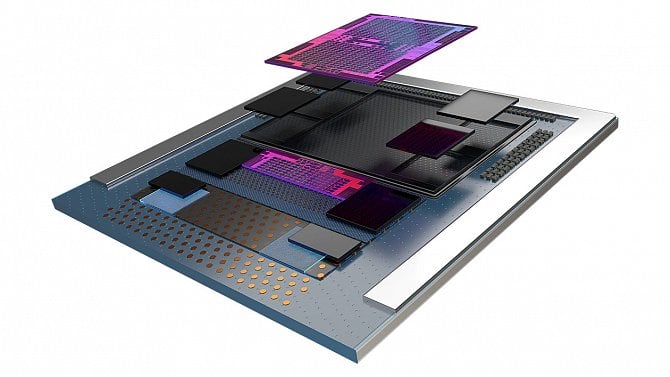

Aldebaran/Instinct MI200 používá paměti HBM2E. To by nebylo nic světoborného, zvlášť u GPU od AMD, ale tentokrát přichází inovace v konstrukci. Předchozí grafiky AMD s HBM nebo HBM2 používaly notoricky známý křemíkový interposer. Nevýhoda je, že pro výkonná GPU musí mít velmi velkou plochu, přitom ale musí být vyráběný jako plnohodnotný, byť primitivní čip. To je i na nějakém starým, třeba 180mm procesu pořád značná rána ve výrobních nákladech (a dnes, když je všech čipů nedostatek, je i spotřeba waferů na velmi starém procesoru značný problém).

Jako třešinka na dortu pak je, že se do interposeru musí vyrábět díry a v nich pak tvořit TSV vodiče pro napojení horního čipu na kontakty substrátu, což vyžaduje další kroky při výrobě (které mohou asi i zvyšovat náročnost a riziko zmetků). Kvůli tomuto jsou GPU a procesory s pamětí typu HBM drahé na výrobu a AMD je eventuálně muselo v segmentu herních grafických karet opustit, přičemž tato technicky zajímavá epizoda možná Radeonům a jejich tržnímu podílu spíš uškodila, než pomohla.

Elevated Fanout Bridge 2.5D

Intel už má nějakou dobu alternativní technologii EMIB, která používá jen malé křemíkové můstky, velké akorát tak, aby provedly vodiče mezi čipem GPU a pouzdrem HBM2, které jsou hned vedle. Toto je mnohem levnější a tím EMIB otevírá cestu pokročilým pamětem (nebo pokročilému propojení jiných čipů) v širším portfoliu produktů – Intel díky tomu mohl mít paměti HBM2 v procesorech Kaby Lake-G. Instinct MI200 přináší poprvé něco podobného také u AMD.

V Aldebaranu už není použitý křemíkový interposer plné velikosti (který by měl asi dost přes 1000 mm²), ale také takové malé a levné křemíkové můstky. Technologie se jmenuje Elevated Fanout Bridge 2.5D a patří patrně jedné z pouzdřících firem, s nimiž AMD spolupracuje (možná by to prý mohlo být SPIL).

Proti EMIB první generace je tato alternativa možná dokonce lepší (ale Intel své technologie dále rozvíjí, takže to neberte tak, že by zde byl předstižen). Zatímco EMIB je zahloubený do substrátu, který tak musí být speciální, Elevated Fanout Bridge 2.5D se osazuje nad substrát, jenž nemusí být nijak přizpůsoben a může být zcela běžný. Je to vcelku jednoduchý trik: můstek, který zajišťuje přemostění dvou čipů, se položí před osazením těchto čipů na substrát (můstek má kontakty nahoře). Protože vyčnívá z plochy, musí čipy být osazené výš než v jeho rovině.

To se provede pomocí měděných pilířů tvořících vycpávku volného prostoru mezi kontakty hlavních čipů a kontakty na substrátu. Tam, kde by normálně byly jen kuličky pájky, jsou tedy jakési sloupky a pájka je na nich. Toto není u AMD nové, měděné sloupky se použily již u procesorů Ryzen 3000 a Epyc 7002, kde ale toliko vyrovnávají rozdíly ve výšce (a v rozměrech kuliček pájky) 12nm a 7nm čipletů.

Přijdou paměti HBM2 konečně i do levnějších GPU nebo APU?

Tato technologie je pořád složitější a dražší než obyčejné zapouzdření běžného monolitického čipu na substrát. Ale měla by už být výrazně levnější a jednodušší než jiné alternativy umožňující osazení pamětí HBM2/2E a také levnější a jednodušší i než ona původní verze EMIB od Intelu. Tudíž tato technologie možná může umožnit tyto rychlé paměti použít ve více i levnějších produktech, i když pomůže jen z části, protože i cena pamětí samotných je vyšší než u DDR4/DDR5 nebo GDDR6.

Z HBM2e nebo budoucí HBM3 by mohla hodně profitovat GPU pro notebooky (tyto paměti mají nižší spotřebu než GDDR), ale také APU/procesory s výkonnou integrovanou grafikou. Pokud by Intel nebo AMD chtěli vyrobit čipy s podobně výkonným iGPU, jaké teď vyprodukoval Apple díky tomu, že se nemusí ohlížet na výrobní náklady, HBM2 by k tomu mohla být cesta.

Více: Apple uvádí procesory M1 Pro a M1 Max: nejrychlejší notebookové CPU, obří integrované GPU

Lék na nevýhody čipletů?

Možná ještě zajímavější ale je, že by se tyto můstky možná mohly použít pro propojení CPU nebo GPU čipletů mezi sebou a mezi IO čipletem a jimi. To by dovolilo zvýšit rychlost takových propojení, možná trošku i latenci. A také by pak komunikace mezi čipy nemusela stát tolik energie navíc. Dnešní čipletové procesory AMD, kde komunikace probíhá přes obyčejný substrát, asi trpí určitou ztrátou výkonu a naopak postihem ve spotřebě, který by provedení těchto propojek skrze můstky Elevated Fanout Bridge 2.5D mohlo zmírnit.

Ostatně, Intel takto hodlá použít EMIB (u procesorů Sapphire Rapids). Tudíž AMD by mohlo z této technologie v procesorech dost benefitovat. Jen nevíme, zda ji tam zkusí nasadit. V poslední době firma preferovala vše dělat hlavně levně a na inovace tohoto typu málokdy vsadila – zřejmě to při objemu výroby nebylo tak rentabilní, jak by bylo třeba, možná šlo i o negativní zkušenost z neúspěchu s Radeony „Fiji“ a „Vega“. Ale kdo ví, třeba teď firma bude schopná tuto inovaci rozšířit i do procesorů Ryzen.

Samotné GPU Aldebaran snad můstky pro komunikaci mezi oběma poloviny GPU ale také ještě nepoužívá, zřejmě jsou použité jen a pouze pro HBM2E. Zde tedy teprve uvidíme, kdy se AMD pokusí otestovat i propojení výpočetních čipletů. U Zenu 4 to asi nebude, protože dosavadní úniky tvrdí, že ten bude ještě mít klasický substrát bez elegantnějšího pokročilého pouzdření (škoda).

Galerie: AMD Instinct MI200 (Aldebaran)

Zdroje: AMD, Tom's Hardware, AnandTech