Odvěcí konkurenti AMD a Intel byli dotlačeni k tomu, aby založili společné konsorcium, která má do budoucna sladit kompatibilitu a nová rozšíření jejich x86 procesorů, zatímco doteď odlišnosti často sloužily jako zbraň proti konkurenci. Na podzim byly představeny technologie, které se takto stanou společným standardem: AVX10/AVX-512, APX, ChkTag, FRED a nově také maticové rozšíření pro AI výpočty ACE, o kterém jsme doteď moc nevěděli.

x86 AI Compute Extensions neboli ACE

Konsorcium x86 Ecosystem Advisory Group teď publikovalo dokument, který ACE (AI Compute Extensions) popisuje a ukazuje, jak bude toto instrukční rozšíření či možná spíše akcelerátor fungovat. Původně jsme očekávali, že ACE bude jenom nové jméno pro technologii AMX. Tu už totiž Intel nějakou dobu má v serverových procesorech, takže by dávalo smysl, vzít ji a standardizovat pro všechna x86 CPU, podobně jako je AVX10 víceméně převzetím původního rozšíření AVX-512.

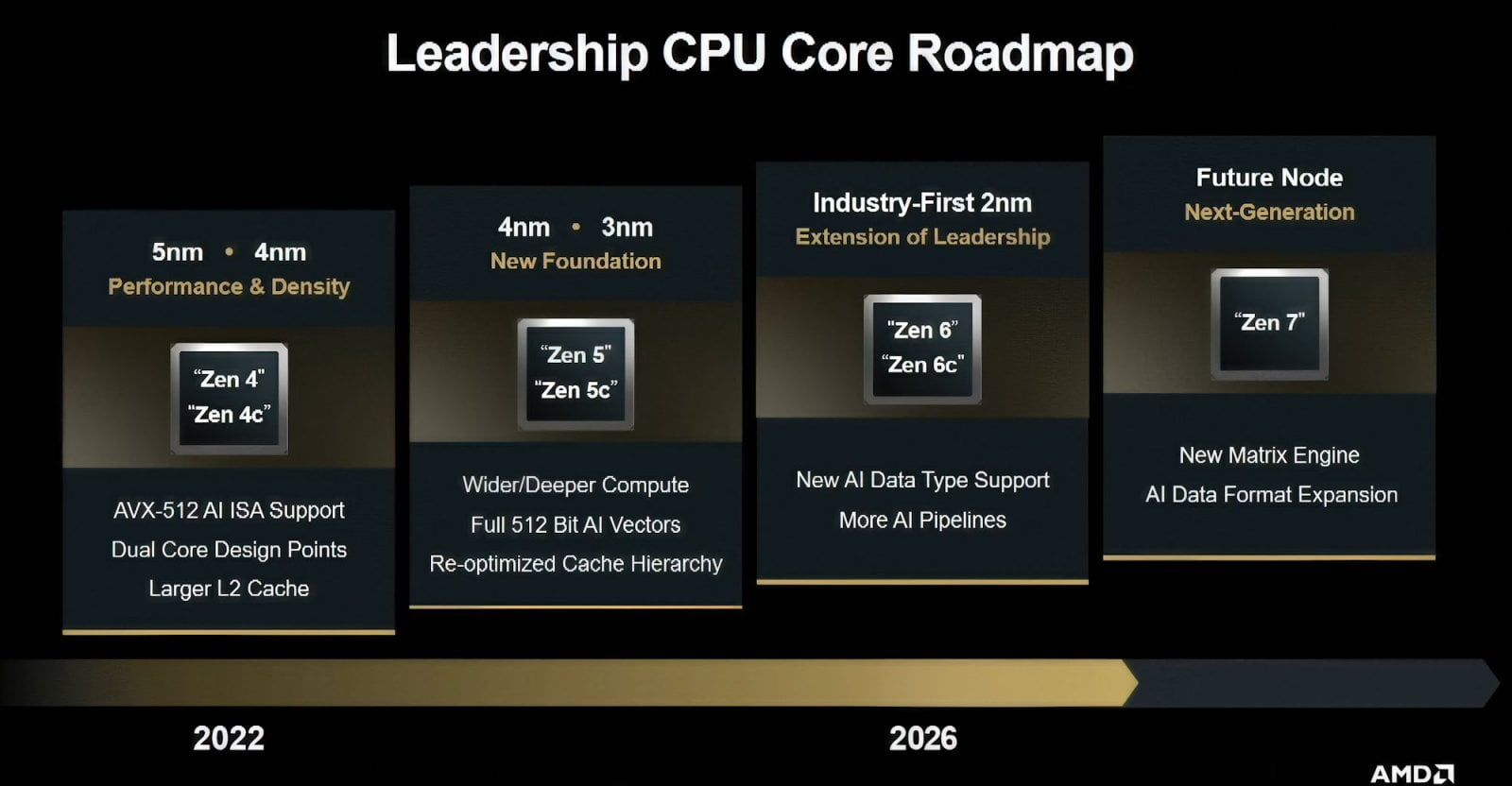

Zdá se ale, že tomu tak není a ACE je nové rozšíření, které nebude s AMX kompatibilní. Je možné, že konsorcium zvolilo alternativní rozšíření, které chystá AMD místo AMX od Intelu (technologii ACE by totiž zřejmě mohla implementovat architektura Zen 7, která má podle oficiální roadmapy přinést rozšířenou akceleraci AI). V dokumentu k ACE se objevuje formulace, podle které se zdá, že hlavním autorem je právě AMD – větší část autorů jsou jeho zaměstnanci. Doposud byla většina novinek v instrukční sadě x86 z dílny Intelu, jelikož větší z konkurentů nad ní měl dominantní kontrolu, teď ale patrně AMD získalo dostatečný vliv, aby mohlo občas jak se říká prosadit svou.

Nicméně ACE bude v nějaké míře naroubováno na to, jak je v instrukční sadě x86 definováno rozšíření AMX a Intel také minimální v pozdější fázi od založení konsorcia x86 Ecosystem Advisory Group do ACE přispíval – takže bez jeho účasti toto nové rozšíření není. Toto navázání (byť nekompatibilní) na ACE by mělo usnadnit přidání podpory do operačních systémů a programování kódu pro nové rozšíření.

AMD připravuje v partnerství s Intelem a x86 EAG (Ecosystem Advisory Group) rozšíření ACE coby standardní architekturu maticové akcelerace pro x86, dál tak rozšiřující vitální ekosystém instrukční sady x86. [překlad: Jan Olšan]

Provázanost s AVX10 (a AVX-512)

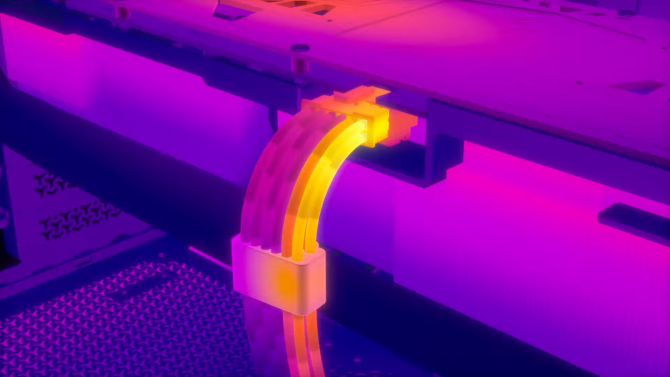

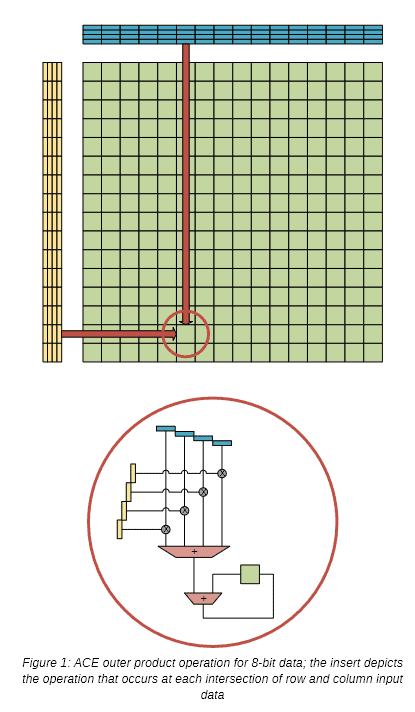

Instrukce ACE jsou určené pro akceleraci operací umělé inteligence, zejména maticového násobení a operace outer product. Specialitou tohoto rozšíření je, že je navrženo k navázání na instrukce AVX-512, respektive AVX10, což jsou 512bitové SIMD instrukce. Rozšíření ACE zavádí nové maticové (dlaždicové) registry, s nimiž pracuje, ale cílem je, aby operace ACE dokázaly v programu přímo spolupracovat s operacemi AVX-512/AVX10 a navazovat na ně.

Schéma operace ACE

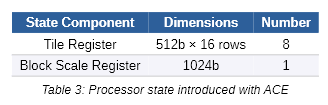

ACE zavádí do instrukční sady x86 osm architektonických „dlaždicových registrů“ (Tile Register), které mají šířku 512 bitů s 16 řádky, takže s 32bitovým datovým typem (pro akumulaci) se v nich dá uložit matice 16 × 16 hodnot. Kromě nich je dále zaveden Block Scale Register, který je jeden a má šířku 1024 bitů. Tyto registry budou novým přídavkem do stavu procesoru, který se musí uložit při přepínání kontextu.

Návrh počítá s tím, že v procesorovém jádru budou tyto nové registry implementovány pomocí stejného fyzického souboru registrů, který se používá pro 512bitové registry ZMM příslušející rozšíření AVX-512/AVX10 – to dovolí efektivně využít infrastrukturu a tranzistory, které už procesorová jádra nainvestovala do AVX-512.

Architektonické registry přidané rozšířením x86 ACE

Operace ACE by měly používat jako vstupy registry ZMM (AVX-512/AVX10) a dlaždicové registry jako akumulátor a výstup. 512bitový registr ZMM pro tento účel (při použití 8bitových hodnot) ukládá čtyři řádky každý s 16 hodnotami. Operace AVX10/AVX-512 se také budou používat pro přípravu vstupů a také bude možné rychle převést výsledky z maticových registrů na SIMD registry ZMM.

V souladu se zaměřením na AI aplikace podporuje ACE výpočty s různými druhy číselných hodnot se sníženou přesností – 8bitový celočíselný INT8, 8bitové floating point formáty OCP FPM8, OCP MXFP8 a MXINT8 a 16bitový Bfloat16. Do budoucna by asi mohly být případně přidané menší formáty. Například FP6 či zejména FP4. Rozšíření ACE obsahuje instrukce pro konverzi z a do těchto formátů, ale nemá instrukce pro přímé výpočty s nimi (zatím).

První podpora v procesorech v roce 2028?

Jak už bylo zmíněno, AMD oznámilo, že procesory Zen 7 budou mít nějaká rozšíření pro akceleraci umělé inteligence. Původně se mělo za to, že půjde o AMX, ale podle všeho do nich AMD chystá právě podporu ACE. Zen 7 má zřejmě vyjít v roce 2028 a mohlo by jít o první nebo jednu z prvních architektur, která výpočty ACE bude poskytovat. A dostat by ji asi mohly všechny varianty jader, tedy i ta v mobilních čipech Ryzen. Dokument uvádí, že podpora ACE půjde napříč x86 procesory – zatímco AMX uměla jen serverová CPU Intel Xeon, ACE má být podporováno v procesorech od serverů po notebooky. Časový horizont podpory v procesorech Intel zatím jasný není.

Roadmapa CPU architektur AMD z Financial Analyst Day 2025 poprvé ukazující Zen 7 mluví o novém maticovém enginu, podle všeho implementujícího ACE

Je asi dobré připomenout, že AMD s Intelem se dohodly i na standardizování instrukcí AVX10 v jejich 512bitové formě pro všechna CPU. Pokud bude možné do jádra s AVX10 díky sdílení fyzického souboru registrů implementovat podporu ACE bez toho, aby stála příliš mnoho tranzistorů navíc, mohlo by toto rozšíření možná být součástí všech x86 jader, místo aby šlo o speciální mimo jádra stojící akcelerátor.

To, že akcelerátor stojí mimo a CPU ho obsahuje v menším počtu než jádra CPU, byl případ například akcelerátoru AMX v procesorech Apple a nyní jednotky SME, která jeho roli přebírá. Apple AMX s AMX od Intelu nesouvisí, avšak plní velmi podobnou obdobnou roli. Tyto jednotky jsou vždy přítomné jen v jednom exempláři v každém klastru jader, která je pak sdílejí.

Zda bude ACE přímo součást jader CPU, je ale něco, co teprve uvidíme – není vyloučeno, že se nakonec jednotka sdílet mezi více jádry pro ušetření plochy na čipu také bude.

Zdroj: x86 Ecosystem Advisory Group