Před časem prosákla zpráva, podle které procesory AMD příští generace s architekturou Zen 6 po dlouhé době zvýší počet jader v jednom CPU čipletu, což také konečně přinese růst počtu jader v desktopových procesorech Ryzen. Nepůjde ale jenom o jádra. Firma také chystá větší L3 cache, což má potenciál zlepšit výkon ve hrách. Zvětšení se přitom týká nejen čipletové 3D V-Cache v dražších procesorech, polepšit by si měly všechny nové Ryzeny.

Jak sdělil youtuber Moore’s Law is Dead (ovšem informace kolovala z nejasných zdrojů už dříve), u procesorů architektury Zen 6 použije AMD tzv. blok CCX s 12 jádry Zen 6. Tento počet jader bude současně také přítomen v jednom CPU čipletu (CCD) desktopových procesorů. Znamená to, že levnější procesory s jedním CPU čipletem, které budou nástupci dnešních Ryzenů 7 9700X, budou mít 12 jader Zen 6. Levnější osekaná verze Ryzen 5 by mohla tím pádem už mohla povýšit na osm jader a naopak dražší modely s dvěma CCD budou mít u nejvyššího modelu 24 jader.

Na internet se teď dostaly informace o serverové verzi Zenu 6, kterou nedávno AMD potvrdilo coby svůj první 2nm produkt a která by asi měla vyjít příští rok. Jde o útržky prezentace AMD s detaily serverových Epyců „Venice“. Sice se tyto detaily netýkají přímo procesorů Ryzen pro osobní počítače, ale nepřímo z nich můžeme čerpat, protože čiplet (nebo návrh bloku CCX) bude pravděpodobně sdílený. Primární informací v nich jsou počty jader, ale pro nás jsou důležité také kapacity cache.

Až 256 jader, Zen 6 stále bez SMT4

Podle tohoto zdroje (na Twitteru uniklé detaily publikoval účet HXL, ale původní zdroj bude na nějakém čínském fóru) má AMD nachystané procesory Epyc 9006 příští generace ve dvou verzích. Procesory s velkými jádry Zen 6 budou mít 8 CCD (po 12 jádrech), což dává 96 jader Zen 6 a 192 vláken. Všimněte si, že jde o snížení počtu CCD, zatímco Epyc 9004 měl 12 CCD a Epyc 9005 dokonce až 16 (a tedy 128 jader). Tím pádem počet jader zůstal relativně konzervativní, AMD zřejmě bude procesory s velkými jádry směřovat spíše k vyššímu výkonu na jedno jádro pomocí frekvencí a zlepšení IPC (výkonu na 1 MHz frekvence).

Podle některých informací se ale maximum 96 jader Zen 6 může týkat jen levnější platformy se socketem SP8 (asi obdoba dnešní SP6). Vedle té má existovat ještě dražší a výkonnější platforma SP7, která by byla následníkem SP5. Je možné, že procesory pro SP7 budou mít i ve verzi s tučnými jádry vyšší počet.

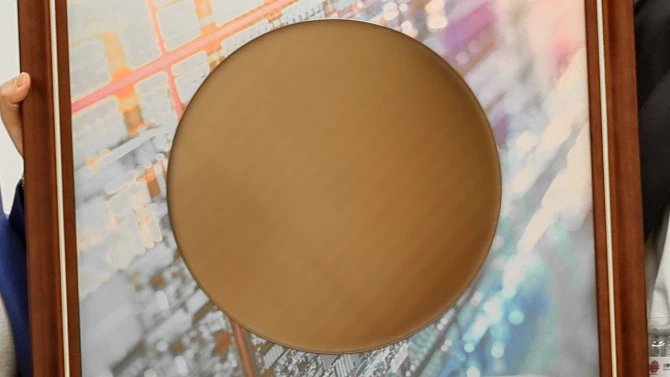

Wafer s 2nm čipy (respektive CCD čiplety) Epyc 9006 Venice

Roli řešení s maximálním výkonem totiž bude zřejmě ještě víc než dnes pokrývat linie procesorů založených na „kompaktní“ či „cloudové“ verzi jádra Zen 6c. Nyní uniklé dokumenty potvrzují, že AMD chystá CCD (CPU čiplety) s 32 jádry Zen 6c. Procesory na nich založené opět budou používat osm CCD, což dá dohromady až 256 jader a 512 vláken – zatím nejvýkonnější procesor, jaký AMD kdy mělo, nynější Epycy 9005 mají nejvýše 192 jader/384 vláken (toto má údajně být procesor pro platformu SP7). Mimochodem, počty vláken byly v uniklých informacích přímo zmíněné.

To znamená, že jádro Zen 6 stále bude používat SMT s dvěma vlákny. AMD tedy tuto technologii bude dále používat, ale nevyzkouší zvýšit současně zpracovávaný počet vláken – na rozdíl od neautorizované(?) evoluce Zenu, která se v Číně na vlastní pěst vyvíjí pod značkou Hygon a která bude v příští generaci techniku SMT4 obsahovat.

Ryzeny dostanou víc L3 cache, důležitá změna pro hry

Čistě informace o počtu jader není pro PC procesory tak důležitá (CCD s 32 jádry Zen 6c se asi na platformě AM5 neobjeví). Ale současně s tím se objevila také informace o L3 cache. Onen 32jádrový CCD má nést 128 MB L3 cache (tedy 4 MB na jedno jádro) a onen základní 12jádrový CCD s jádry Zen 6 obsahuje 48 MB. To znamená, že základní Ryzeny 5 a Ryzeny 7 s jedním CCD budou také téměř určitě vybaveny 48 MB L3 cache, tedy o 50 % větší, než mají dnes (32 MB). Toto by se mělo měřitelně projevit na herním výkonu analogicky k přínosu, který má cache u X3D procesorů. Modely s dvěma CCD budou mít celkem 96 MB L3 cache, ale je to ve dvou blocích, takže to nebude mít stejný efekt jako monolitická 96MB L3 cache u procesorů Ryzen 7 5800X3D / 7800X3D / 9800X3D.

Vedle toho ale AMD zvětší i kapacitu cache, kterou budou disponovat X3D procesory, protože se zvětší i kapacita SRAM na přídavném čipletu s cache. Podle leakera Keplera_L2 také zde dojde k navýšení o 50 %, tedy z dnešních 64 MB na 96 MB. Podle toho, jak se vše zvětšuje o stejný faktor, je to zřejmě vše vedeno zachováním symetrie mezi počty jader a bloky / banky cache). Následník herního Ryzenu 7 9800X3D tedy zřejmě bude mít 12 jader Zen 6 (24 vláken) a k tomu 144 MB L3 cache. I u něj by navýšení o 50 % mělo přinést další nárůst výkonu ve hrách, zejména u těch, jejichž „hot data“ jsou větší a do dnešní 3D V-Cache se nevejdou. Zlepšit by se mohla i latence a plynulost.

Některé tituly, které mají sadu nejčastěji používaných dat poměrně malou a ideálně se vejdou do 96 MB dnešních X3D procesorů, může pokrok být menší, je asi možné, že se projeví zákon klesajícího užitku. Ale tam, kde nyní objem cache nestačí, mohou zase nastat výraznější zlepšení. S časem komplexnost a „velikost“ her roste, takže zvětšování cache bude mít přínos už jenom proto, že bude tento trend podchycovat. Příští generace procesorů AMD by tímto každopádně měla být zajímavá pro hráče.