Další generace procesorů AMD s novou architekturou Zen 6 se očekává až druhé polovině příštího roku a zatím se k němu teprve začínáme dozvídat detaily. Je proto velká věc, že se teď dostaly ven první informace už o Zenu 7, což bude následující generace, která by měla být velkým předělem. Přišel s nimi youtuber Moore’s Law is Dead a zatím je asi třeba brát je s rezervou, ale jejich obsah chtě-nechtě stojí za pozornost.

Zen 7 je ve skutečnosti pět různých jader?

Zen 6 nebude koncepčně zcela nový, má sice přinést velké změny v čipletové stavbě a „uncore“, ale jádra CPU budou evolučně navazovat na Zen 5. Má to být právě jádro Zen 7, které by zase mělo být radikálnějším přepracováním architektury. A možná i způsobu, jakým AMD vůbec postupuje. Podle Moore’s Law is Dead, který se odvolává na údajné interní dokumenty firmy, chystá AMD se Zenem 7 značnou změnu. Tato architektura má mít bezprecedentní množství různých verzí. AMD s tímto opatrně začalo u jader Zen 4c a 5C, která jsou optimalizovaná na menší plochu výměnou za horší frekvence.

U Zenu 7 to ale má jít dál. Vedle jader Zen 7 „Classic“ (tedy velké jádro, které se liší optimalizacemi vyladěnými na míru konkrétnímu procesu, které mu dovolují dosáhnout vysokých taktů) a kompaktního jádra Zen 7c „Dense“ ještě další dvě nebo tři. Z „Dense“ jader, která už známe dnes, dokument chce vyrobit ještě další specializace – Zen 7 „Low Power“ a Zen 7 „Efficiency“. Tato jádra by se lišila tím, že by už neměla stejnou architekturu jako je tomu u Zenu 7c, jenž se liší jen fyzickou optimalizací a z ní vyplývající frekvencí.

Verze „LP“ a „E“ by už měly například zredukované počty jednotek nebo možná zkrácené některé fronty a další úpravy, která jádro zjednodušují a zeslabují. Šlo by tedy o v pravém slova smyslu malá jádra, byť vyvinutá na společném základě s velkým. Jádro Low Power by mířilo na co nejnižší spotřebu a zabranou plochu, jádro „E“ zase na energetickou efektivitu (čímž se myslí co nejlepší poměr mezi výkonem a spotřebou).

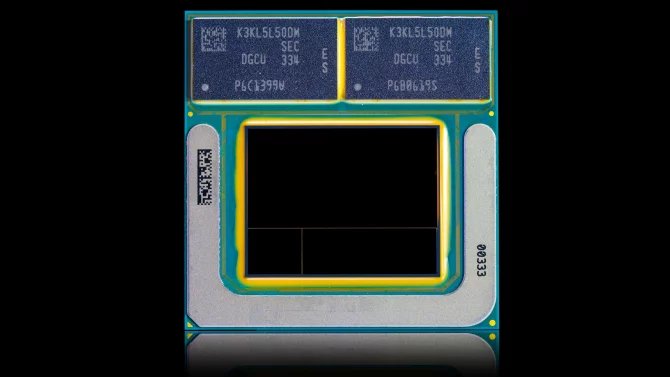

Dokument ještě zmiňuje variantu „3D Core“. O té si Moore’s Law is Dead myslí, že už půjde o přechod k plně 3D čipletové stavbě procesorů, kdy celé jádro je vícevrstvé. Teoreticky by ale toto označení mohlo mluvit jen o už dnes známých procesorech s 3D V-Cache a nešlo by tedy o nějakou radikální novinku. Podle Moore’s Law is Dead to ale tak není a jde o radikálnější přechod k vrstvené architektuře, kde by mohlo být více čipletů položených na sobě použito i k nahuštění logických obvodů a výpočetních prostředků, nejen cache. Pokud by toto Zen 7 přinesl, byla by to přelomová novinka v návrhu procesorů – tento koncept se sice už dlouho diskutuje, ale zatím spíše bez realizace.

Výrobní proces a vydání: V roce 2027, nebo spíš později?

Podle Moore’s Law is Dead AMD chystá výrobu procesorů s architekturou (nebo už možná je třeba mluvit o architekturách) Zen 7 na velmi pokročilém výrobním procesu – na technologii A14 (1,4nm procesu) od TSMC. O té jsme psali nedávno, jde o další „next-gen“ úroveň následující po teprve přicházejícím 2nm procesu. Je zajímavé, že AMD se zatím vyhne technologie Backside Power Delivery (ta je použitá v 1,6nm procesu A16). O těchto budoucích procesech jsme psali zde:

Na 1,4nm procesu mají být ovšem vyrobené jen CCD čiplety, případné IO čiplety budou na nějakém starším. I čiplety s 3D V-Cache mají prý používat 4nm proces TSMC. Je zajímavé, že podle MLID prý AMD chce provést tape-out už v říjnu 2026, z čehož vyvozuje, že by procesory mohly být vydané koncem roku 2027 nebo začátkem roku 2028. Jenže – samotné TSMC start výroby na procesu A14 zatím plánuje v roce 2028, takže Zen 7 může vyjít nejdříve v té době. Možná ale spíš i později, protože AMD nebývá v aplikaci nejnovějších technologií mezi prvními.

A je zde vždy možnost, že se tento výrobní proces ještě i opozdí proti plánu. Připomeňme, že Moore’s Law is Dead podobně tvrdil, že AMD použije proces N2X pro Zen 6, jenže TSMC samotné pak sdělilo, že tato technologie bude dostupná až o rok později a AMD potvrdilo použití jen základní verze procesu N2. Zde může jí to podobný omyl (nebo informaci z dokumentů, které už dávno nejsou aktuální).

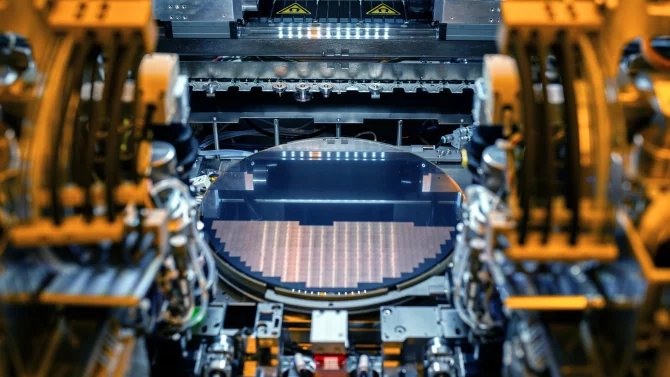

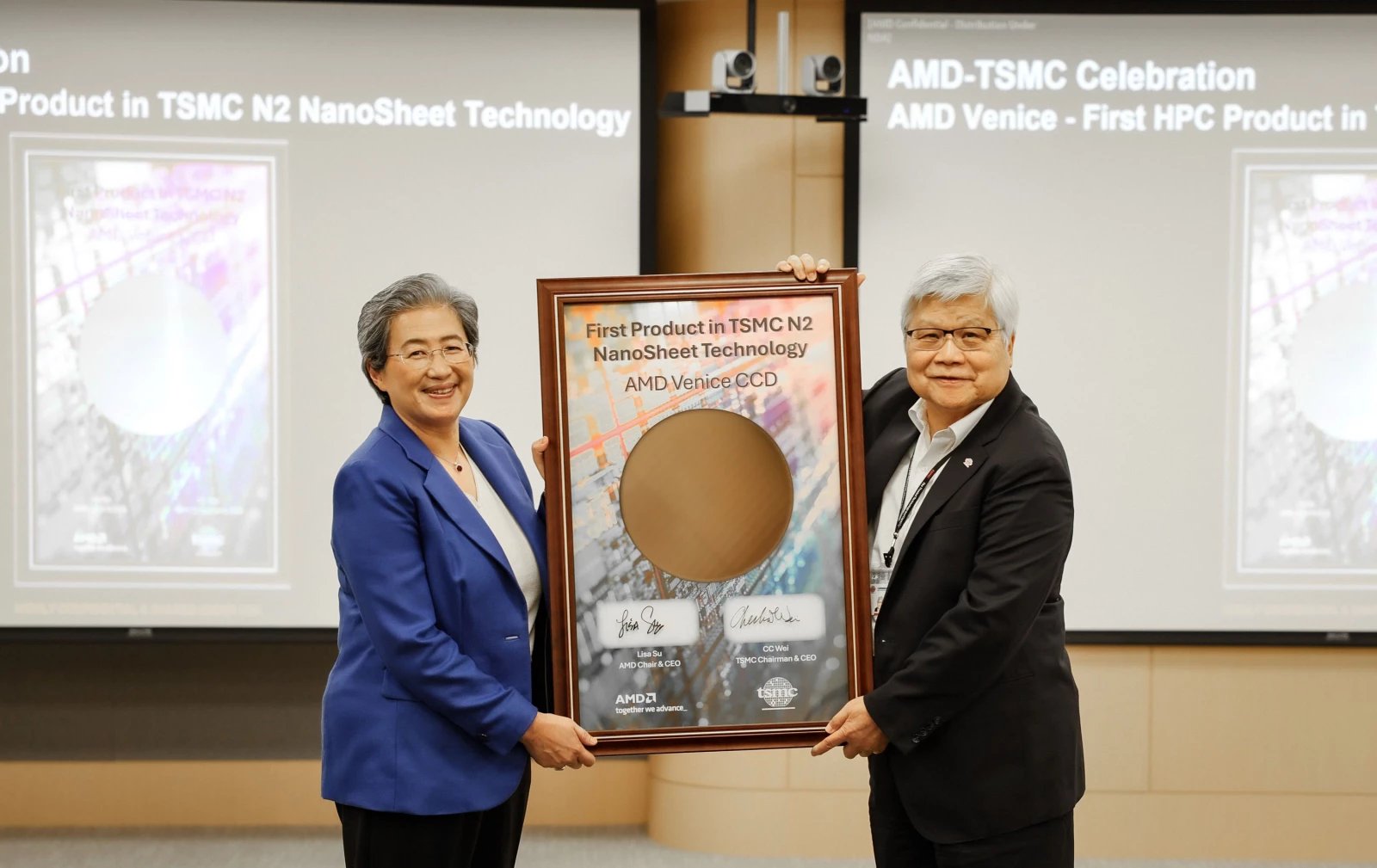

Šéfka AMD Lisa Su a šéf TSMC C. C. Wei předvádějí wafer s 2nm čipy (respektive asi čiplety) Epyc 9006 Venice

IPC jádra Zen 7, větší cache

Zen 7 má údajně mít větší L2 cache s kapacitou 2 MB. Zajímavé je, že L3 cache má mít poněkud nepravidelnou kapacitu 7 MB na jedno jádro (teoreticky by mohlo jít o 8 MB s tím, že osmina by byla vyhrazená pro nějaký jiný účel a nebyla by viditelná pro software) v separátním cache čipletu. To znamená, že hypotetický čiplet s 12 jádry by měl 84 MB V-Cache. Zda všechna L3 cache bude jen v separátním čipletu, nebo zda by k těmto 7 MB bylo něco navíc i v základním čipletu s jádry, to možná ještě není jisté.

Moore’s Law is Dead také tvrdí, že má informace o interních výkonnostních cílech. AMD prý plánuje, že Zen 7 přinese při stejné frekvenci oproti zenu 6 nárůst výkonu na 1 MHz (tedy tzv. „IPC“) o +15–25 %. Interní cíl je prý dosáhnout většího než +20% nárůstu IPC v benchmarku SPECINT17. Nejpíš toto číslo platí pro jádra Classic, ale řečeno to přímo není. Připomeňme, že dle uniklých plánů AMD má Zen 6 mít IPC o něco přes 10 % vyšší proti Zenu 5 (poznámka: IPC se ale liší aplikaci od aplikace, tato čísla budou vždy jen průměr z nějaké sady programů).

33 jader?

V těchto informacích je ještě jedno atypické číslo. AMD prý u Zenu 7 plánuje integrovat 33 jader na jeden CPU čiplet. Toto liché číslo je ale asi snadno vysvětlitelné – AMD zdá se v čipletu bude mít jádra ve třech řadách po 11. Teoreticky je možné, že většina produktů bude mít jedno jádro vždy vypnuté pro zvýšení výtěžnosti a v praxi se tedy tento čiplet bude chovat jako 32jádrový.

Vysoký počet jader bude asi dosažený dvěma cestami. Jednak asi půjde o „Dense“ jádra Zen 7c, tento čiplet totiž bude používaný v serverových procesorech, zatímco v Ryzenech se asi neobjeví. Také ale má používat ono čipletové řešení, kdy by zřejmě všechna L3 cache byla lokalizována v separátním čipletu s 3D V-Cache vespod v odpovídajícím půdorysu o třech řadách (šlo by o ony zmíněné 7MB bloky L3 cache – možná, že kapacita je tedy daná tím, co bude sedět k ploše jádra v horní vrstvě). Dnes tvoří L3 cache okolo poloviny plochy CPU čipletů, takže její eliminace by měla dovolit přidat na křemík CCD až dvojnásobek jader.

V serverových procesorech Epyc s jádry Zen 7 bude údajně použitý stejný IO čiplet jako v pro Zen 6, který bude mít nový design. Obě generace tedy budou v serverech používat stejný socket (respektive sockety SP7 a SP8).

Do vydání těchto procesorů ještě zbývá dlouhá doba. U podobných úniků vždycky platí, že je třeba je brát opatrně, protože nelze vyloučit omyly nebo že někdo pouze spekuloval. V tomto případě ale také může dojít k tomu, že třeba podobné plány existují, ale budou ještě do roku 2028 změněny nebo zrušeny. Tudíž nelze zaručit, že se všechny tyto věci u zenu 7 opravdu potvrdí.

Zdroj: Moore’s Law is Dead