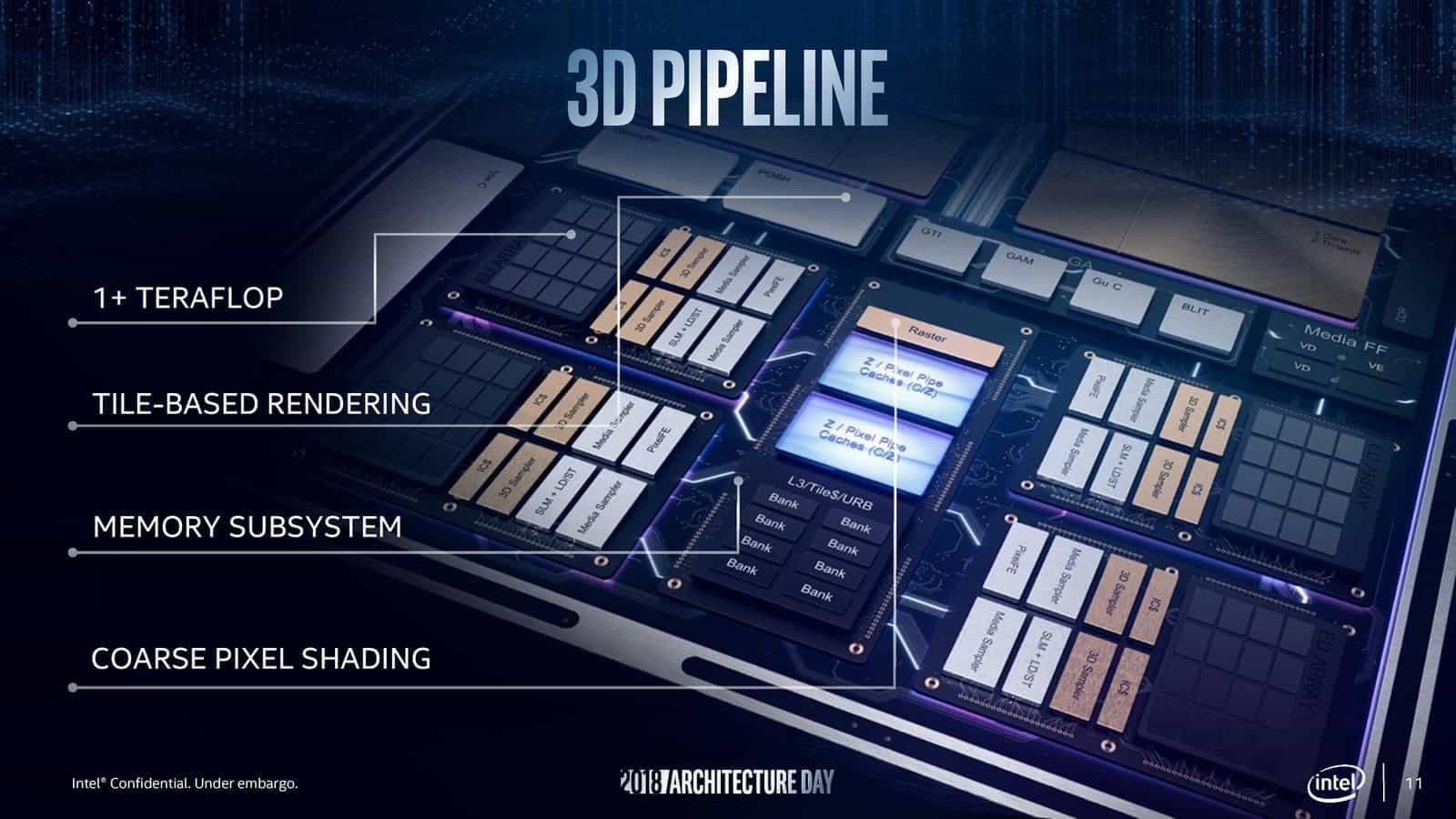

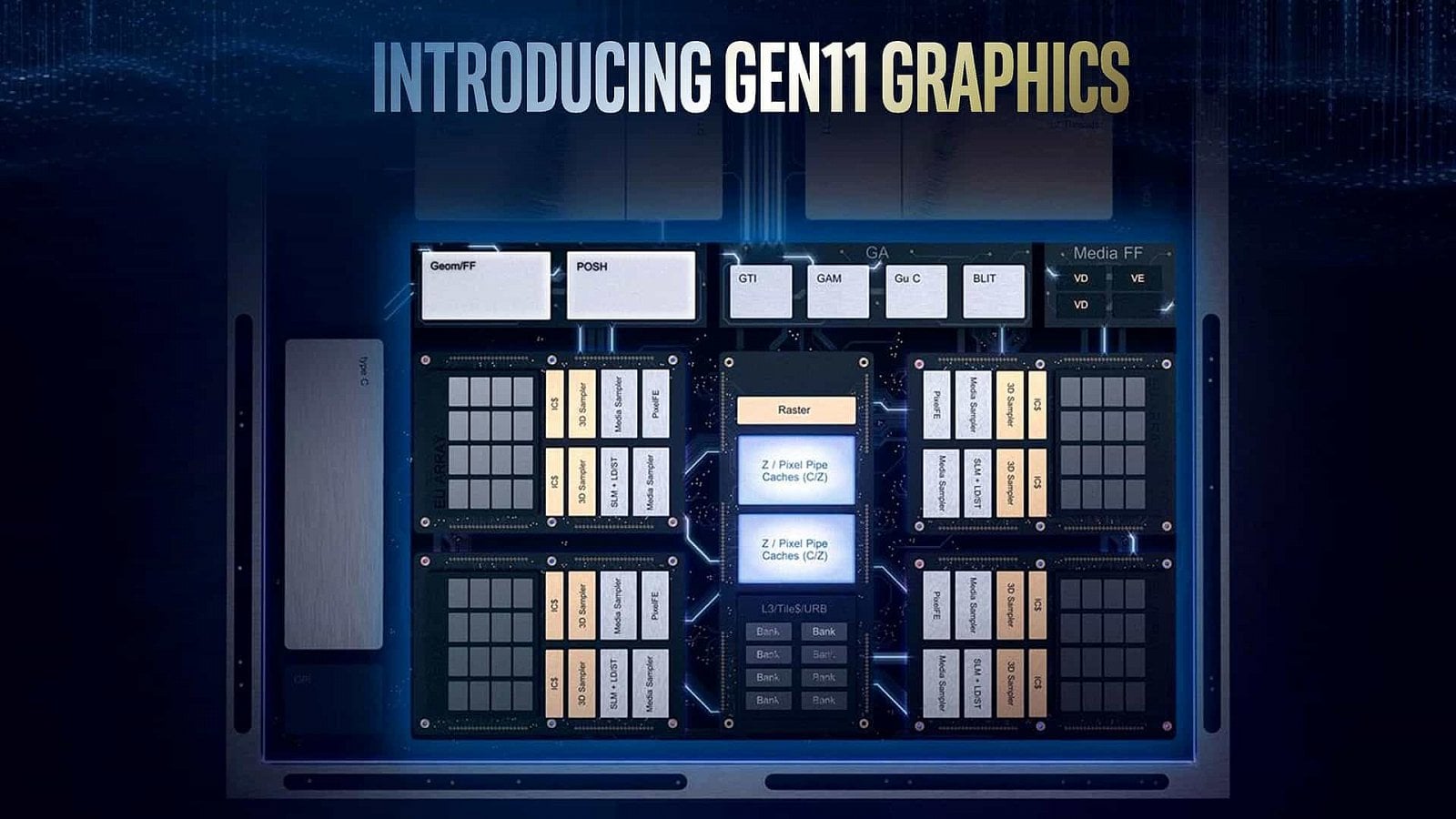

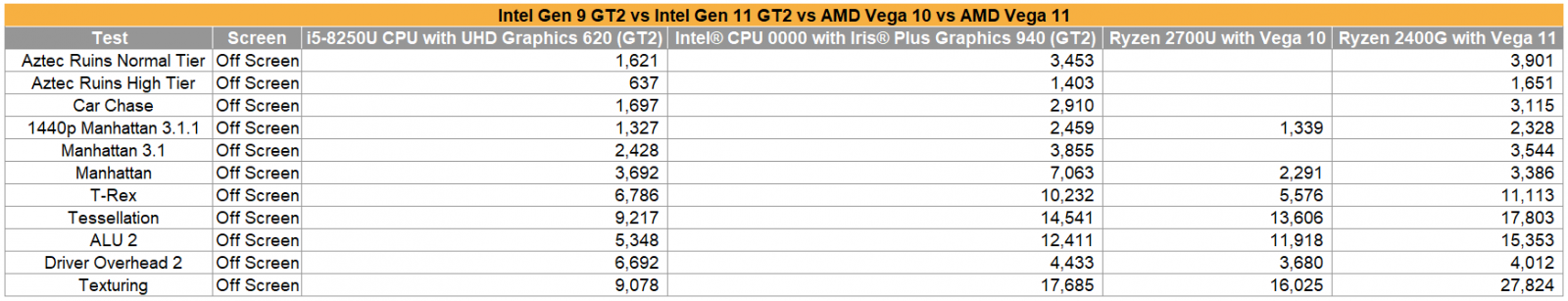

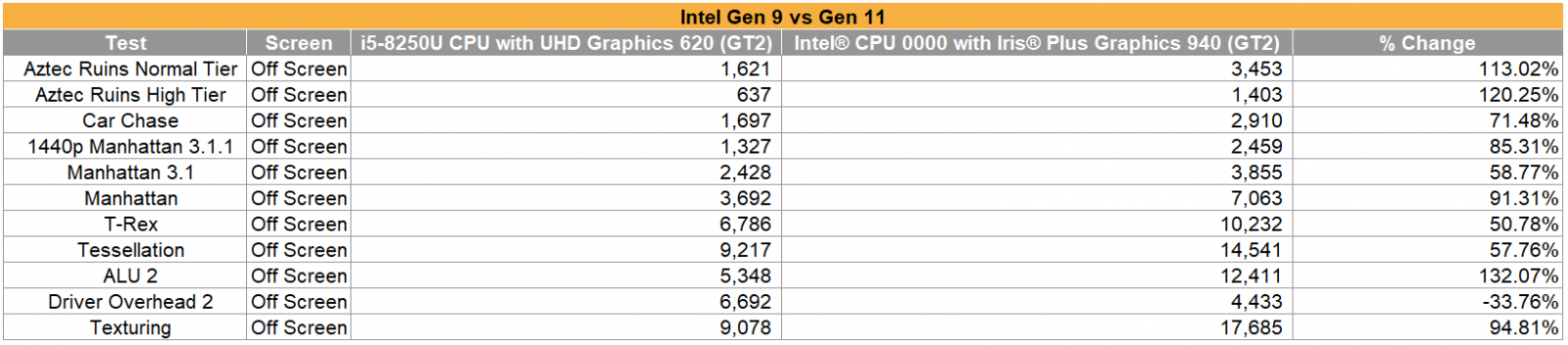

Vypadá to, že Intel chystá velkou architektonickou změnu svých GPU. Letos firma vydala v 10nm procesorech Ice Lake novou poměrně výkonnou integrovanou grafiku Gen11 s řadou nových technologií, ovšem její koncepce vychází stále z linie předchozích GPU Intelu. V následující generaci procesorů Tiger Lake s architekturou „Gen12“ ale zdá se nastane zásadní zlom a inovace vnitřností. Což je zajímavé i proto, že tato architektura půjde do prvních samostatných GPU Intel.

Gen12: jedna z největších změn od roku 2006

O grafikách Intelu se poměrně dost informací objeví předem, protože firma publikuje s velkým předstihem otevřené Linuxové ovladače. A to platí i pro Tiger Lake, které přijde na trh až příští rok. Patch přidávající podporu pro grafiky Gen12 má poměrně dlouhý vysvětlující komentář, v němž stojí podstatná věc. Gen12 má údajně představovat masivní změnu v instrukční sadě, s kterou GPU pracuje. A to opravdu velkou, údajně je předěláno kódování téměř všech instrukcí, operací a registrů. Podle vývojáře, který patch zaslal, jde o jednu z největších změn od příchodu grafické architektury i965 (podle níž se jmenuje současný Linuxový ovladač, podporující všechny následující GPU).

Pokud se nepletu, ona architektura i965 přišla na svět v roce 2006 s desktopovým čipsetem G965 pro procesory Intel Core 2 (GPU bylo tehdy v externím severním můstku čipsetu spolu s řadičem pamětí). Samotná integrovaná grafika se jmenovala Intel GMA X3000 a poprvé plně hardwarově zpracovávala shadery, zatímco předchozí generace architektury používaly pro řadu činností softwarovou emulaci. Od tohoto jádra, podporujícího DirectX 9.0c a OpenGL 2.1, se táhne linie grafik Gen5 (Nehalem), Sandy Bridge (Gen6) a tak dále až po Skylake/Kaby Lake (Gen9/9.5) a teď Ice Lake. Samozřejmě se při tom zvyšoval výkon, schopnosti a počty jednotek.

Gen12 is planned to include one of the most in-depth reworks of the Intel EU ISA since the original i965. The encoding of almost every instruction field, hardware opcode and register type needs to be updated in this merge request.

Nicméně Gen12 s Tiger Lake má být zásadní zlom. Jednak v instrukční sadě, kterou dlouho Intel udržoval kompatibilní – možná proto, že v ovladačích a multimediálním enkodéru/dekodéru Quick Sync se používá hodně kódu manuálně napsaného a optimalizovaného přímo pro tuto instrukční sadu GPU. Nyní u Tiger Lake se kompatibilita po dlouhé době přetne, což bude příležitost k moha interním změnám, které by měly posunout výkon a schopnosti dál. Současně dost možná tato nová instrukční sada opět může být základ pro další dlouhou postupnou evoluci.

Zjednodušení architektury jednotek pro lepší výsledný výkon

Ovšem instrukční sada je pořád do určité míry jen vnější obraz toho, co se děje uvnitř. Linuxový ovladač ale odhaluje i jednu zásadní interní změnu. Intel chystá značné zjednodušení mikroarchitektonické implementace výpočetních jednotek. Bude odbourána tzv. logika Register Scoreboard, s jejíž pomocí výpočetní jednotky garantovaly koherenci obsahu registrů mezi čteními a zápisy. To znamená, že už nebude vždy 100% bezpečné k registrům přistupovat, hardware nebude automaticky garantovat, že například při čtení nemůže dojít k vrácení nesprávné hodnoty kvůli tomu, že mezitím do registru byl proveden další zápis. Aby nedošlo k takovému konfliktu čtení a zápisů (jehož výsledkem jsou nesprávná data), bude tedy místo hardwaru muset hlídat samotný běžící software, potažmo jeho kompilátor.

But probably the most invasive change is the removal of the register scoreboard logic from the hardware, which means that the EU will no longer guarantee data coherency between register reads and writes, and will require the compiler to synchronize dependent instructions anytime there is a potential data hazard (…)

Toto může znít jako zhoršení, ale ve skutečnosti takové zjednodušení výpočetní jednotky pravděpodobně je přínos a cesta k lepšímu výkonu. Odstraní se z ní totiž určitá komplexita, kterou převezme softwarová vrstva (kompilátor se postará, aby na sobě závisející operace byly provedené ve správném pořadí). A na oplátku by zjednodušený shader/EU snad mohly lépe škálovat – dosáhnout lepší frekvence, potřebovat méně tranzistorů a tím umožnit integraci více jednotek na GPU.

Zjednodušení může otevírat cestu k vyššímu výkonu

Zejména by asi toto zjednodušení mohlo vést ke zlepšení energetické efektivity. A právě ta je jedním z hlavních klíčů ke škálování výkonu GPU, jelikož TDP je vedle velikosti čipu jeden z hlavních limitů samostatných (ale eventuálně i integrovaných) grafik. Pokud se tedy při stejném výkonu sníží spotřeba jedné jednotky, vede to k vyššímu celkovému výkonu u výsledných grafik. Podobné zjednodušování výpočetních jednotek během jejich evoluce prováděla například i Nvidia.

Vypadá to tedy, že v mnoha ohledech Intel u architektury Tiger Lake/Gen12 provedl cosi jako vyčištění a odstranění nánosů a bude u ní opět začínat s čistým stolem, i když asi jen částečně, o kompletní start na zelené louce asi také úplně nejde (to je však dost vzácná věc). Toto by samozřejmě mohlo integrovaným grafikám Tiger Lake a následujících procesorů (po Tiger Lake má být Alder Lakes grafikou Gen13 a CPU jádrem Golden Cove, zřejmě stále na 10 nm) dost prospět.

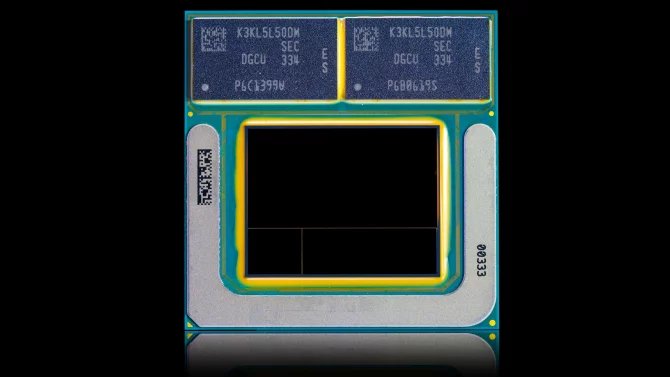

Začátek vývoje grafik Xᵉ

Ještě důležitější to ale asi je proto, že na Gen12 bude firma stavět první samostatná GPU. Intel si tedy zvolil okamžik pro odstranění zpětné kompatibility a „bagáže z minulosti“ chytře. Samostatné grafiky, u nichž by také měl přijít nový důraz na herní výkon, tak budou od počátku nová kontinuita, což by mělo být přínosné pro dlouhodobý vývoj ovladačů. Ovšem jak tento projekt Intelu celkově dopadne, to zatím pořád nemůžeme vědět, čeká ho určitě nejedno další úskalí.