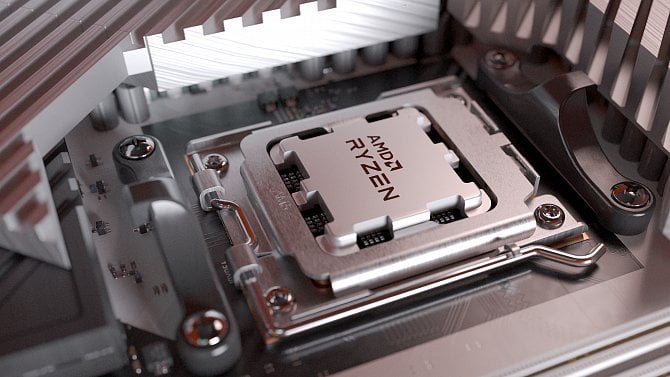

Víc než napjatá jsou asi očekávání, která jsou nyní vkládána do procesorové architektury Zen 2, kterou AMD vypustí na trh příští rok. Zatímco Zen loni vrátil firmu do hry, jeho druhá generace bude muset dokázat, že nešlo o nějakou jednorázovou deviaci a AMD dokáže táhnout vývoj čím dál náročnějších čipů a architektur dál. A to i když se Intel probere z určitého útlumu, do kterého se dostal vlivem opožděného 10nm procesu a možná i relaxace na vavřínech. AMD o Zenu 2 doteď zarytě mlčelo, ale včera konečně nastal čas pravdy a firma poprvé prezentovala, co od nové architektury můžeme čekat. Máme tak první detailní informace o 7nm procesu, architektuře jádra Zen 2 a mimochodem také hodně výživnou polévku o druhé generaci serverových CPU Epyc, které novou architekturu budou používat.

Zen 2: (o dost?) lepší architektura a IPC

Hned z kraje AMD potvrdilo, že Zen 2 nebude nějaký lehký refresh architektury prvního Zenu, ale naopak opravdu větší přepracování, o kterém lze mluvit jako o nové architektuře. Jádro bude mít vyšší IPC, i když firma nesdělila o kolik, takže nelze potvrdit ani vyvrátit nedávné drby o „13 %“. AMD možná včera neodhalilo všechny změny, které se chystají, ovšem vylepšen zdá se bude jak „backend“ výpočetních jednotek, tak frontend, tedy infrastruktura, která jim přiděluje práci.

Jádro Zen 2 má mít zdokonalenou predikci větvení (což je něco, co bývá vylepšováno kontinuálně a tedy prakticky v každé nové architektuře). Zároveň má být lepší i přednačítání dat do paměti neboli prefetch. Obě tato zlepšení by měla znamenat, že procesor bude efektivněji využívat výpočetní jednotky. Jelikož méně často poběží naprázdno, mělo by se zvýšit IPC. AMD také údajně zlepšilo instrukční L1 cache a zároveň byla zvětšena kapacita Mikro-OP cache pro dekódované instrukce. Tato cache byla jedním z hlavních zlepšováků architektury Zen a její optimalizování by tedy opět mohlo slušně pomáhat.

256bitová FPU: vysoký nárůst výkon pro multimédia

A nyní zcela zásadní zlepšení v Zenu 2: AMD potvrdilo, že toto jádro spraví jednu z hlavních slabin Zenu proti jádrům Intelu – jen 128bitové výpočetní jednotky SIMD neboli FPU. Zen 2 jejich šířku zdvojnásobí na 256 bitů. Takže instrukce AVX a AVX2 budou prováděné v jednom průchodu a jejich výkon se teoreticky až dvakrát zvýší. Toto by mělo značně zrychlit zejména enkódování videa (x264, výrazněji x265) a jiná multimédia, ale také HPC zátěže, kde měl díky širšímu SIMD Intel velkou výhodu. Syntetické testy měřící jen výkon SIMD by měly mít nárůst až o 100 %.

AMD zároveň zdvojnásobilo propustnost load/store pipeline, takže ani přísun (a odsun) dat z jednotek by neměl výkonnější výpočty brzdit, protože jeho kapacita také úměrně vzroste. Mělo by to znamenat, že šířka dat, které load/store jednotky budou číst a ukládat do L1 cache (a pak do L2 a RAM) se rozšíří ze 128 bitů na 256 bitů. Počet jednotek load/store se asi nezmění.

Zvýšena byla také propustnost jádra ve fázích dispatch (odesílání instrukcí do jednotek) a retire (finální fáze ukončující práce na konkrétní instrukci). Díky těmto a předchozím změnám má tedy Zen 2 schopen prohánět skrze jádro více operací za cyklus i mimo SIMD operace. AMD také u jádra zachová dvoucestné SMT, jedno jádro tedy bude umět počítat dvě vlákna naráz.

V prezentaci také bylo zmíněno, že by Zen 2 měl mít i bezpečnostní přínosy. Bude vylepšeno šifrování paměti a (což už bylo oznámeno dříve) opraví se některé bezpečnostní díry odhalené tento rok. Některé varianty chyby Spectre budou ošetřené přímo v hardwaru. Výsledkem všech těchto faktorů má být každopádně jak vyšší IPC – tedy výkon při konkrétní frekvenci – jádra Zen, tak také údajně vyšší celkový výkon (jak výrazně, to je samozřejmě ještě tajné).

7nm proces: poprvé lepší než Intel?

Není novinka, že Zen 2 se bude vyrábět na 7nm procesu, a již také není překvapením, že bude použitá výroba u TSMC (GlobalFoundries již vyvinutý 7nm proces neuvede do produkce). Firma včera sdělila některé charakteristiky této technologie. Má údajně dosahovat až o 25 % vyšší výkon při stejné spotřebě, případně při stejném výkonu o polovinu nižší spotřebu. Hustota tranzistorů může být až dvojnásobná (pravděpodobně proti 14nm procesu GlobalFoundries). Je ale třeba nevztahovat tato čísla na celé CPU, v tom se totiž zvyšuje komplexita architektury a počet tranzistorů, takže spotřeba je nakonec obvykle stejná a nárůst frekvencí je přesto obvykle nižší.

Mimochodem, AMD zařadilo do prezentace slajd naznačující, že 7nm proces TSMC by mohl docílit lepšího poměru spotřeby k výkonu, než jaký bude mít Intel. Původně se prý čekalo, že by 7nm technologie mohla vést k určité paritě nebo k téměř plné eliminaci náskoku, který Intel má. Zpožďování a snad i horší než očekávané výsledky 10nm procesu Intelu ale prý naznačují, že by se situace dokonce mohla obrátit a 7nm technologie od TSMC by mohla být energeticky efektivnější. Prakticky poprvé by tak konkurence měla výhodu lepších (respektive aspoň efektivnějších) tranzistorů.

Článek pokračuje na další straně odhalením 64jádrových procesorů Epyc generace Rome.

Rome, Epyc druhé generace: zatím nejkomplexnější procesor AMD

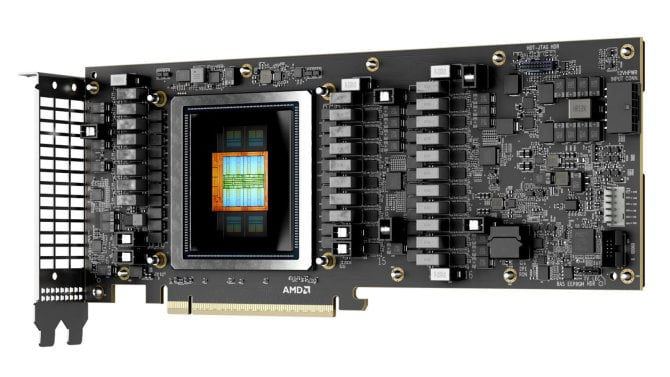

AMD zároveň poprvé poodhalilo serverové procesory Epyc druhé generace s kódovým označením Rome, což bude první produkt, který přinese jádra Zen 2 a také 7nm proces u CPU. Tedy částečně, jak hned uvidíte, bude to docela divočina připomínající některé velmi komplexní „big iron“ procesory. Potvrdily se totiž dříve hodně neuvěřitelně znějící zprávy o tom, že AMD tyto procesory složí zatím bezprecedentně modulárním přístupem. Už nebude používat MCM pouzdro se čtyřmi křemíky, které by byly současně používané v desktopové platformě AM4. Epyc Rome bude místo toho složen z osmi (až osmi, nižší modely jich použijí méně) malých 7nm čipů s jádry Zen 2.

To ale ještě není vše. Tyto miničipy či čípky („chiplety“) mají zdá se obsahovat jen samotná jádra CPU, proti 14nm generaci tedy nebudou schopné samostatné existence. V každém z těchto kousků bude osm jader, takže celkově bude mít Epyc druhé generace až 64 jader, dvojnásobek toho, co první Epyc s 32 jádry. Zatím nevíme, jak budou jádra členěna, zda stále do čtyřjádrových bloků CCX, nebo nějak jinak.

Pomocí logiky Infinity Fabric (respektive její druhé zřejmě vylepšené generace) budou čípky s jádry CPU propojené s devátým centrálním čipem, který bude vše koordinovat a spojovat dohromady. V tomto čipu (který podle fotek bude docela obří, podobá se highendovému GPU) budou společně sdružené řadiče pamětí DDR4, PCI Expressu a dalšího I/O, jakož i další společná infrastruktura, northbridge/southbridge a vše ostatní, co SoC potřebuje. Je možné, že by zde mohla být obsažena i nějaká sdílená cache poslední úrovně (L3 nebo možná spíš L4).

Tento čip bude pomocí propojovací logiky Infinity Fabric druhé generace komunikovat s jádry CPU v 7nm čipech, sám bude ovšem 14nm. Tato technologie je podle AMD optimálnější pro implementování I/O funkcí. O konkrétní výbavě toho nebylo řečeno, ale víme, že kanálů DDR4 je osm a řadiče PCI Express už umí verzi PCIe 4.0 s dvojnásobnou propustností.

Toto vše bude tedy tvořit složitou soustavu rovnou devíti čipů. Propojené budou zřejmě standardním substrátem, nejde o 2,5D pouzdro s křemíkovým interposerem, jaké mají GPU Fiji nebo Vega. I tak ale asi výrobní náklady budou o dost vyšší a výroba složitá. Ovšem zvenku bude mít čip stále pouzdro SP3 s osmikanálovým řadičem a stejnou konektivitou PCIe jako první generace Epyců (jen s rychlejšími linkami). Rome tedy bude kompatibilní s existujícími servery, bude stačit aktualizovat BIOS. A pozor. Ve stejné platformě bude fungovat i následující generace Milan s jádry Zen 3, AMD to výslovně slíbilo.

První nástřel výkonu: 2× rychlejší na socket

Vzorky Epycu Rome už delší dobu existují a fungují. AMD uznalo za vhodné zařadit do prezentace i jejich demo a podělit se i o nějaký hrubý příslib výkonu. 7nm Epycy s 64 jádra mají mít dvakrát vyšší výkon na jeden socket proti dnešním 32jádrům. To znamená, že výkon v přepočtu na jedno jádro neklesne i přesto, že aplikace bude muset vytížit dvakrát více vláken a normálně zde platí zákon klesajícího užitku. Nicméně toto asi znamená, že frekvence serverových Zenů 2 budou asi pořád nízké jako u 14nm Epyců, možná i nižší (okolo 2 GHz v základu).

Nicméně nebylo řečeno, v jako disciplíně toto poměřování spočívá (nejde-li jen o prostý počet jader). Floating Point výkon a SIMD ovšem díky širším jednotkám SIMD budou mít zlepšení dvojnásobné, až 4× vyšší výkon na jeden socket.

Jeden Rome proti dvěma Xeonům Platinum 8180M

AMD také ukázalo demo 7nm Epycu se 7nm GPU Radeon Instinct, kde platforma ukázala více než dvojnásobný výkon při klasifikaci obrázků. Zajímavější ovšem byl test přímo procesorů. AMD postavilo jeden 64jádrový Epyc proti 2S serveru se dvěma Xeony Platinum 8180M, tedy s nejvýkonnějšími procesory Skylake-SP, které Intel nyní má – tento server měl tedy 56 jader.

Na obou byl spuštěn 3D rendering v C-Ray (používající jádra CPU) a systém s jedním procesorem Epyc byl schopen tuto úlohu dokončit dříve, než dvousocketový systém s highendovými Xeony. A to za 27,7 sekundy proti 30,5 sekundám u Intelu. Epyc měl sice převahu v počtu jader, takže být rychlejší o 9,2 % není úplný zázrak, ale pravděpodobně měl výrazně nižší spotřebu, což je třeba vzít v úvahu. Xeon Platinum 8180M má TDP 205 W, což je více než 180 W u Epyců první generace. I pokud by AMD zvýšilo u 64jádra TDP třeba na 250 W, stále by to znamenalo, že má mnohem lepší poměr výkon/watt.

Je třeba ještě dodat, že šlo jen o prototyp, nikoliv finální čip. Jakožto ES vzorek pravděpodobně testovaný procesor měl nižší takty, než s jakými se Rome bude prodávat – možná o dost. Podle informací z prezentace nebyl přetaktován a používal vzduchové chlazení. Nicméně na druhou stranu je také C-Ray úloha, která podobně jako třeba Cinebench velmi sedí už architektuře Zen, takže představuje cosi jako ±ideální případ (pro srovnání, dva 32jádrové Epycy 7601 jsou v tomto testu hotové za 28,1 sekundy). Ovšem pokud budou výsledné takty výrazně vyšší než u tohoto ES, může 1S server s procesorem Rome porážet pár nejsilnějších Xeonů i v mnoha dalších zátěžích.

Vydání až příští rok

Kdy tyto procesory přijdou na trh, AMD zatím nesdělilo. Stále tedy platí jen údaj „někdy v příštím roce“. Osobně bych asi čekal uvedení v polovině roku nebo v třetím kvartále, ale je možné že firma ještě překvapí. Kdy se jádro Zen 2 dostane i mimo servery do Ryzenů, to zatím také přesně netušíme, ale podle AMD to bude „velmi brzy“ po vypuštění Epyců. Komplexní kombinace 7nm a 14nm čipu v oblasti PC asi vhodná nebude, takže pro desktopové Ryzeny AMD pravděpodobně bude muset navrhnou odlišný, monolitický čip. kolik jader takový Ryzen 3000 bude moci mít, tudíž zatím vůbec netušíme.