Intel před nedávnem v koordinaci s AMD oznámil návrat k výkonným SIMD instrukcím k AVX-512, které zmizely z procesorů Core pro PC kvůli hybridní architektuře s E-Core. Teď máme potvrzeno, že zpátky budou už v nových 2nm CPU, která vyjdou příští rok. Jejich jádra dostanou zpět schopnost zpracovávat 512bitové vektorové instrukce, které byly jedním z prvků úspěchu procesorů AMD s architekturami Zen 4 a Zen 5, byť jsou paradoxně od Intelu.

S AVX-512 to přes jeho renesanci v rukou AMD chvíli nevypadalo dobře. Intel totiž oznámil jiné SIMD instrukce AVX10, které měly být nástupcem, ale v podstatě přecházely na poloviční 256bitovou šířku. Intel totiž počítal s tím, že 512bitová šířka vektorů AVX10 (což by byl téměř přesný ekvivalent AVX-512 pod novým jménem) bude nepovinná a jen v serverech.

Ovšem loni se věci začaly měnit. Oba výrobci s dalšími subjekty ustavili konsorcium pro koordinaci a společný vývoj instrukční sady a platformy procesorů x86 a jedním z výsledků bylo, že 256bitová verze AVX10 byla zrušena. Zůstalo jenom AVX10 s plnou 512bitovou šířkou, které je v podstatě ekvivalentní AVX-512. V budoucnu tak budou stejné SIMD instrukce umět jak procesory Intel, tak AMD. A nebude to vůbec trvat dlouho, podle informací, na které upozornil InstLatX64 na bývalém Twitteru.

AVX-512 / AVX10.2 bude v Nova Lake

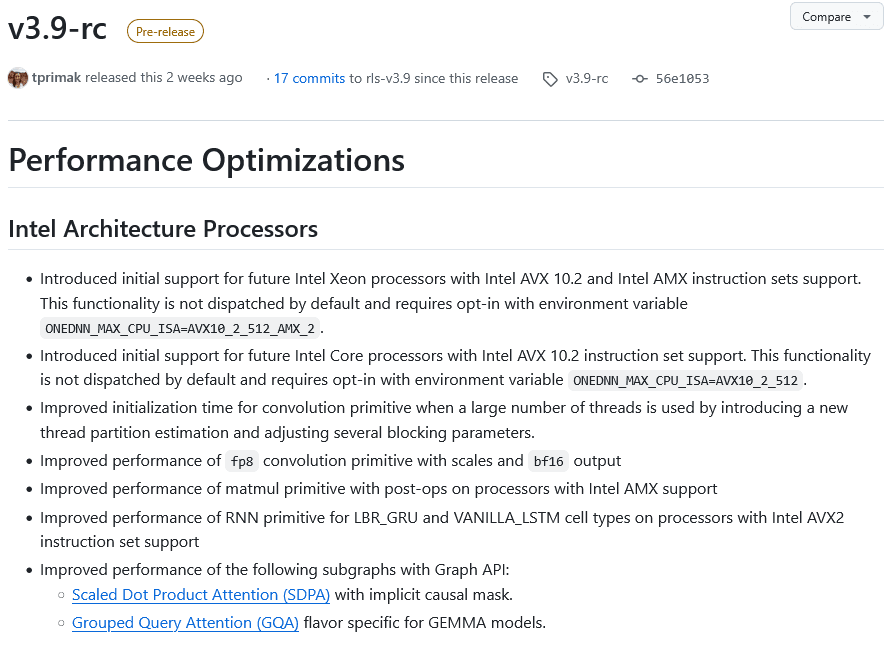

V kódu přidaném do projektu oneDNN, což jsou knihovny pro aplikace umělé inteligence používající technologie oneAPI od Intel, byla teď přidána pro AVX10.2 s 512bitovou šířkou práv pro nadcházející CPU. Vydání 3.9 přidává podporu pro použití AVX 10.2 (s 512bitovou šířkou – „AVX10_2_512“) a maticových instrukcí AMX na serverových procesorech Xeon, u nichž by mělo jít o generaci Diamond Rapids. Patche zřejmě vychází z interních informací, které potvrzují přítomnost těchto instrukčních rozšíření na dotyčných CPU.

Na stejném místě ale je potvrzená také přítomnost AVX10.2 s 512bitovou šířkou už i v klientských procesorech Core (respektive asi Core Ultra), tedy procesorech pro notebooky a desktopová PC. Ty nedostanou AMX, ale AVX 10.2 s 512bitovou šířkou neboli AVX-512 ano. A má jít už o příští generaci procesorů s kódovým označením Nova Lake, která má vyjít příští rok jako řada Core Ultra 400.

Poznámky k vydání oneDNN v3.9-rc uvádějící podporu AVX-512 na procesorech Intel

AVX10.2 s 512bitovou šířkou (a tedy plnohodnotnými 512bitovými registry ZMM) je prakticky ekvivalentem AVX-512, změny by měly být jen kosmetické, nebo v podobě nově přidaných instrukcí. Tyto procesory by proto automaticky měly mít i kompatibilitu s původním AVX-512 a aplikace bude možné psát tak, aby byly kompatibilní s jejich původním subsetem. Ač je tedy řeč o AVX10, znamená to i AVX-512.

V desktopových PC bude Nova Lake používat nový socket LGA 1954 a má přinést procesory s až 52 jádry (16 P-Core, 32 E-Core a 4 LP E-Core v SoC čipletu). Vedle nich mají existovat i procesory s méně jádry (8 P-Core, 16 E-Core, 4 LP-Core), ale s velkou cache, tzv. BLLC, pro herní počítače. Ty by mohly konkurovat X3D procesorům od AMD.

Výkon bude záležet na architektonických detailech

Jak bude podpora AVX-512 a AVX10 implementována, není zatím známo. Instrukce budou určitě už mít i jádra E-Core, u těch to ale nejspíš bude implementace na 256bitových SIMD fyzických jednotkách, které budou 512bitový vektor zpracovávat ve dvou průchodech, jak je tomu u jader Zen 4 od AMD (a také u jader Zen 5 v notebookových procesorech Ryzen AI 300 – s výjimkou Ryzenů AI Max, které mají plné 512bitové jednotky).

Zda bude takováto 256bitová implementace použitá i u jader P-Core, těžko říct. Jejich využití v serverech by asi mohlo motivovat přidání plně 512bitových jednotek. Výkonnostní charakteristika by se sice lišila, ale to mezi jádry P-Core a E-Core platí tak jako tak, nemusí to tedy být na překážku.

Zmíněné procesory AMD s architekturou Zen 4 ukázaly, že i 256bitová implementace AVX-512 má značný výkonnostní přínos pro procesory, které tyto instrukce dovedou využít, takže Nova Lake může být i s hybridní architekturou slušnou platformou pro takové aplikace.

A důležité je, že po přidání těchto instrukcí do E-Core už zřejmě všechny nové x86 procesory Intelu budou toto instrukční rozšíření mít (a ty od AMD také). Skončí tak skoro deset let neblahé fragmentace, kdy AVX-512 podporovala jen malá část drahých CPU, což omezovalo ochotu vývojářů tyto instrukce používat v programech. To by se do budoucna mohl změnit.

Jak dobře bude AVX-512 na Nova Lake fungovat, bude samozřejmě záležet na detailech, nelze to úplně předvídat. Důležité bude například, jak budou zpracovávané shuffle instrukce, které potřebují ideálně speciální jednotku s plnou šířkou. Zen 4 takové jednotky má a dokáže i 512bitové permutace provádět velmi rychle. Pokud by například jádra E-Core v Nova Lake na tomto místě šetřila, mohly by na nich shuffle instrukce mít nízký výkon (například kvůli latenci několika cyklů a nízkém počtu operací zpracovatelných za jeden cyklus). To by pak mohlo v některých aplikacích kazit přínosy z podpory AVX-512. Doufejme, že architekti jader pro Nova Lake pod tlakem AMD přijdou s něčím dobrým.

Zdroje: InstLatX64, oneDNN