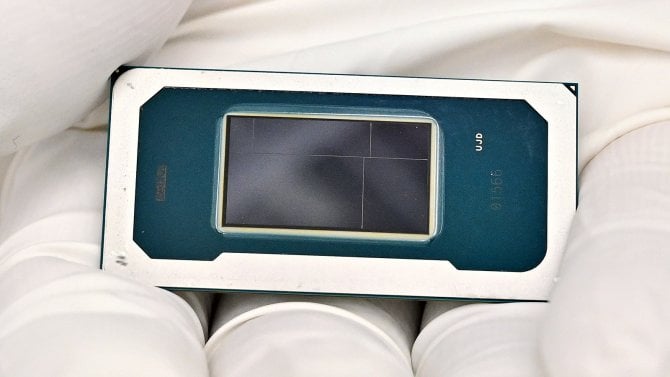

Jak asi víte, Intelu se poněkud zkomplikovaly plány budoucích procesů kvůli zpožděné dostupnosti 10nm procesu. Nedávno se dokonce objevily zvěsti, že musel být kompletně zrušen, které ale firma hned popřela. První 10nm produkty proto musely být nahrazeny dalšími 14nm čipy, což se kromě PC (teď s osmijádry Coffee Lake Refresh) týká i serverů. Intel byl problémem s 10nm procesem přinucen k neobvyklým řešením, takže nyní přichází s něčím, co dosud nepraktikoval – vícečipovými („MCM“) procesory.

Cascade Lake-AP: lepidlo nyní i od Intelu

Jako konkurenci pro současné či asi hlavně nadcházející 7nm procesory AMD Epyc oznámil polovodičový gigant procesory Cascade Lake „Advanced Performance“ (Cascade Lake-AP). Ač ještě před rokem firma MCM řešení v prezentacích pro média shazovala jako „slepenou“ náhražku, která je horší než monoliticky čip, nyní toto řešení aplikuje také. Xeony Cascade Lake totiž budou přesně jako Epyc slepené z více čipů v jednom pouzdře.

Cascade Lake-AP budou ovšem na rozdíl od Epyců zřejmě tvořené ne čtyřmi, ale jen dvěma čipy (takže srovnatelné to bude spíše s dřívějšími Opterony řady 6000). Motivace je patrně taková, že na 14nm procesu už by kvůli velikosti křemíku Intel nebyl schopen přidat další jádra v dostatečném počtu. Dvojčipový Cascade Lake-AP ovšem bude mít až 48 jader. Tedy 24 na čip. Ale jelikož asi používá stejný 14nm křemík Cascade Lake-SP jako příští generace standardních Xeonů (má opět obsahovat 28 jader), asi by zde ještě mohla být rezerva ke zvýšení až na 56 jader. Ovšem Intel ji nemusí využít, je možné, že 2 × 24 jader bylo shledáno jako optimum kvůli spotřebě.

12kanálové paměti

Výhoda plynoucí ze „slepence“ bude, že procesor bude moci použít paměťový řadič obou křemíků. Cascade Lake-AP bude totiž mít 12kanálový řadič pamětí DDR4, tedy asi 12 nebo 24 slotů DIMM na jeden socket. Měly by tedy podporovat dvojnásobek paměti RAM proti dnešním Xeonům Scalable (Skylake-SP) pro platformu LGA 3647. Na jeden socket by to bylo 3 TB se 128GB moduly nebo 6 TB s novými 256GB moduly.

Toto logicky znamená, že musí být použitý jiný socket, v zákulisních zprávách se objevilo označení LGA 5903. Rozměr pouzdra by tak asi mohl být hodně velký. Procesor je podle všeho ekvivalentem dvou standardních Xeonů v jednom, čipy jsou uvnitř propojené sběrnicí UPI běžící substrátem CPU. Je to tedy řešení velmi podobné tomu od AMD, není použito nějaké pokročilejší zapouzdření s interposerem ani technologie EMIB. Jeden Xeon Advanced Performance je tak ekvivalentem dvousocketového serveru. Zřejmě to také znamená, že maximální konfigurací bude asi 4S sestava (místo 8S u Xeonů Platinum). V materiálech, které Intel ukázal, se mluví o 2S (dvousocketových) serverech s těmito MCM procesory, které se reálně budou chovat jako 4S. Konfigurace 2S by asi mohla být nejčastější.

Výkon 48jader Cascade Lake-AP by měl podle Intelu být velmi vysoký. Dvouprocesorová sestava (tedy s dvěma dvoučipovými procesory) s celkem 96 jádry má proti dvousocketovému serveru s Epycy 7601 (což je nejrychlejší model od AMD s 32 jádry) mít až 3,4× vyšší výkon v Linpacku (HPC floating point výpočty s využitím AVX-512) a až 1,3× vyšší výkon v Stream Triad.

Proti nejrychlejšímu jednočipovému Xeonu Platinum 8180 má Cascade Lake-AP být rychlejší 1,21× v Linpacku, v Stream Triad pak 1,83× (tento benchmark by měl testovat efekt paměťové propustnosti, tedy zde dvojnásobného počtu kanálů paměťového řadiče). Protože architektura Cascade Lake má nové instrukce pro vyšší výkon v operacích strojového učení, mají Cascade Lake-AP v těchto úlohách být až 17× rychlejší než Xeon Platinum 8180 (Skylake-SP). Cascade Lake má jinak také opravené některé bezpečnostní díry, z čehož bude verze AP samozřejmě také profitovat.

Výzvy: spotřeba, cena, velikost

Více podrobností a parametrů zatím Intel nesdělil. Zatím tedy těžko říct, jak vysoká například bude cena, ale také zůstává tajemstvím TDP. Spotřeba bude asi docela zásadní, protože už jednočipové Xeony Platinum mohou mít TDP i přes 200 W. Cascade Lake-AP bude tedy buď mít hodně velký příkon na socket, nebo snížené takty, což by ale také snižovalo výkon.

Kromě toho bude také zajímavé vidět, jak rozměrné bude pouzdro. Už socket SP3 pro Epycy dělá výrobcům desek problémy, je zdá se hodně náročné na jednu serverovou desku dostat dva sockety a dvakrát 16 slotů DIMM pro paměti, aby byly možnosti řadiče DDR4 plně využity. Zde bude 2S server potřebovat 2×24 kanálů a prostor vyhrazený pro CPU bude možná ještě větší. Je možné, že 2S servery budou realizovány dvěma propojenými deskami, nebo u nich bude nutné osazovat jen 12 slotů pro RAM na socket (tedy jen jeden DIMM na kanál). Bude asi docela zajímavé vidět, jak si výrobci desek a Intel s návrhem pouzdra a PCB poradí.

Velké ryby už mají vzorky

Reálné uvedení na trh nastane u těchto CPU až příští rok (2019), dnešní oznámení je tedy jen papírové. Vydání by mělo nastat ve stejný den, jako u standardních Xeonů Cascade Lake-SP. Ovšem vzorky a rané verze těchto procesorů již existují, Intel sdělil, že privilegovaní velcí zákazníci typu Amazon/Google už v rámci raného přístupu procesory Cascade Lake-AP dostávali již v třetím čtvrtletí.